半導體 (Semiconductor)

解決方案與軟體

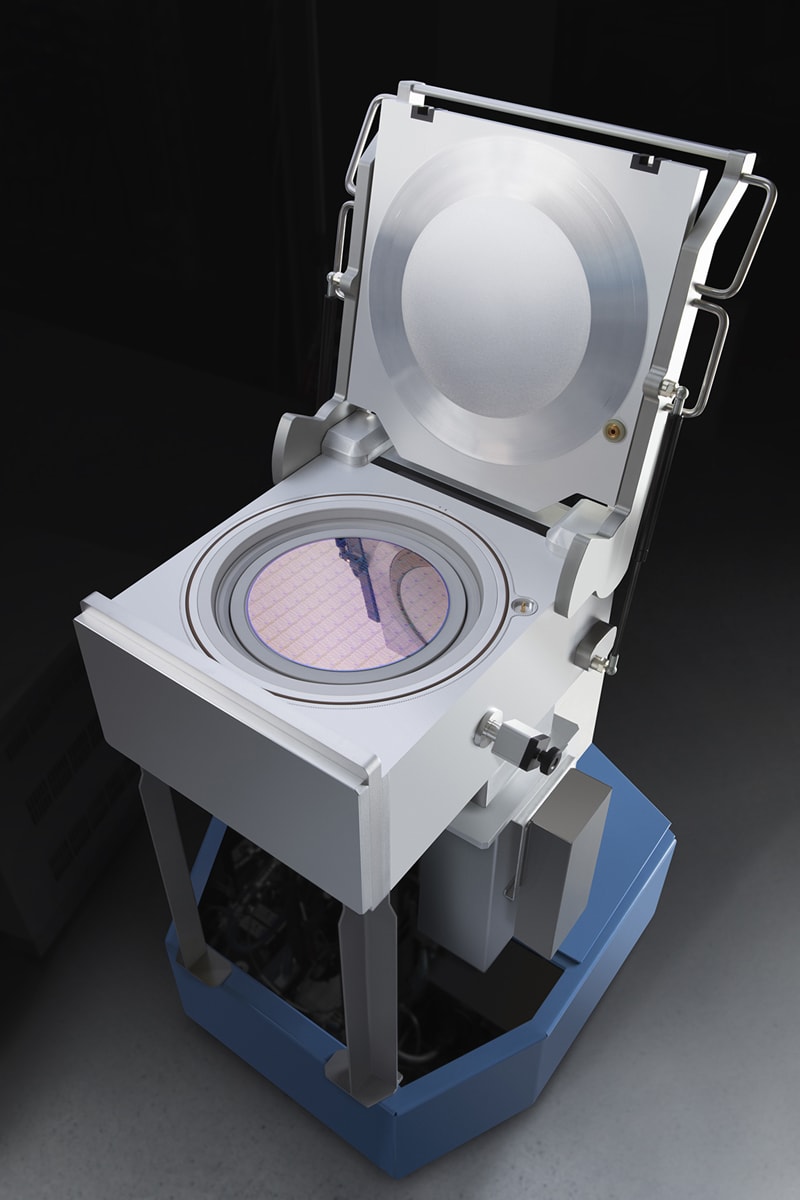

Centura iSprint SSW ALD/CVD

鎢的電阻率低,電遷移性極小,長期以來一直運用在邏輯製程和記憶體元件中,用作填充接觸點和中段 (最底層) 的導電層連接 (將電晶體與積體電路其餘部分相連) 的首選材料。在早期技術中,由於元件尺寸較大,因而可以使用 CVD 均勻沉積法進行鎢填充整合。不過,在當前最先進的技術下,元件尺寸極微小且呈凹形輪廓,很難使用這種沉積法來確保對這些線寬進行完好的無縫隙鎢填充。由於沉積期間超小開口頂部周邊會出現懸垂現象,使得均勻製程無法完好填充出無孔洞的線寬;即便不產生孔洞,均勻沉積法也不可避免會在中間留下縫隙。這些屬性使得極微小線寬容易在化學機械平坦化 (CMP) 期間遭到破壞;先進晶片設計中的高線寬密度以及缺乏導孔冗餘,意味著一個簡單的孔洞就會造成元件故障和良率損失。

Centura™ iSprint™ ALD/CVD SSW 系統融合了應用材料公司在材料工程和金屬 CVD 接觸點應用領域長期積累的專業能力和豐富經驗,利用獨特的「選擇性」抑制機制,可由下而上進行無縫隙或無孔洞的填充。改善填充的完整性,有助於提高鎢體積 (有可能降低電阻),製造出更堅固耐用的線寬,並可緩解對介電質和蝕刻開口步驟的要求,從而改善效能、元件設計和良率。

點選此處了解更多資訊。

Centura iSprint SSW ALD/CVD 系統利用獨特的「選擇性」抑制機制,是業界第一個達到由下而上的 CVD 鎢間隙填充、完全無縫隙或孔洞。該系統使鎢體積最佳化,製造出更耐用的線寬,有助於提高良率。