半导体 (Semiconductor)

解决方案与软件

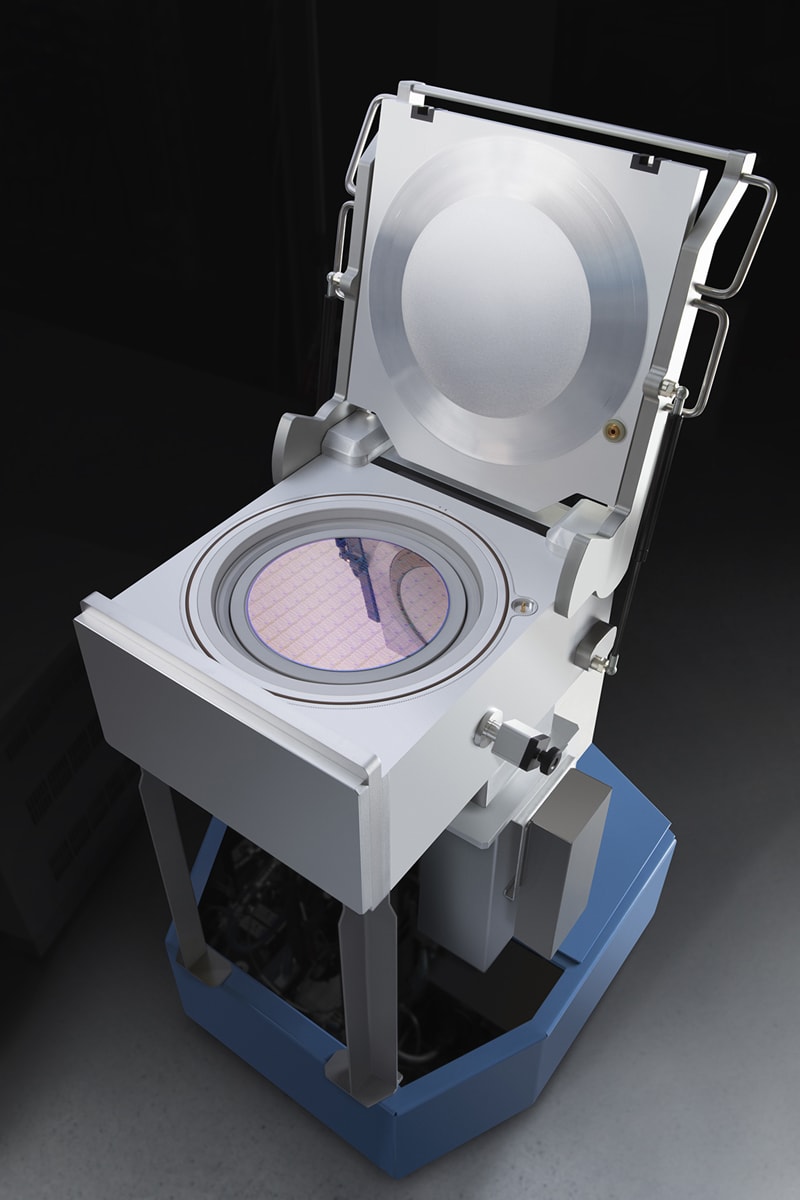

Centura iSprint SSW ALD/CVD

钨的电阻率低,电迁移性极小,长期以来一直在逻辑和存储器件中用作接触孔和中段(最底层)连接线(将晶体管与集成电路其余部分相连)的首选填充材料。在早先的技术节点中,由于器件尺寸较大,因而可以使用共形 CVD 沉积法进行钨填充集成。不过,在当前最先进的技术节点下,特征尺寸极其细微,而且还有凹形形貌,因而难以使用这种沉积法来确保对这些器件特征进行完好的无缝隙钨填充。由于沉积期间超小开口顶部周边会出现悬垂现象,使得共形工艺无法完好填充出无孔洞的特征;即便不产生孔洞,共形沉积法也不可避免会在中间留下缝隙。这些属性使得极其细小的特征结构容易在化学机械抛光 (CMP) 期间遭到破坏;先进芯片设计中的高密度特征以及缺乏通孔冗余,意味着一个简单的孔洞就会造成器件故障和成品率损失。

Centura™ iSprint™ ALD/CVD SSW 系统融合了应用材料公司在材料工程和金属 CVD 接触孔应用领域长期积累的专业能力和丰富经验,利用独特的“选择比”抑制机制,自底向上进行填充,避免出现缝隙或孔洞。改进填充工艺的完整性,有助于提高钨体积(有可能降低电阻),制造出更坚固耐用的特征结构,缓解对介电质和刻蚀开口步骤的要求,从而改善性能、器件设计和成品率。

点击此处了解更多信息。

Centura iSprint SSW ALD/CVD 工艺利用独特的 “选择比” 抑制机制,提供业内第一个自底向上的 CVD 钨间隙填充工艺,填充后不会出现缝隙或孔洞。该系统优化了钨体积,可制作出更结实耐用的特征结构,有助于提高成品率。