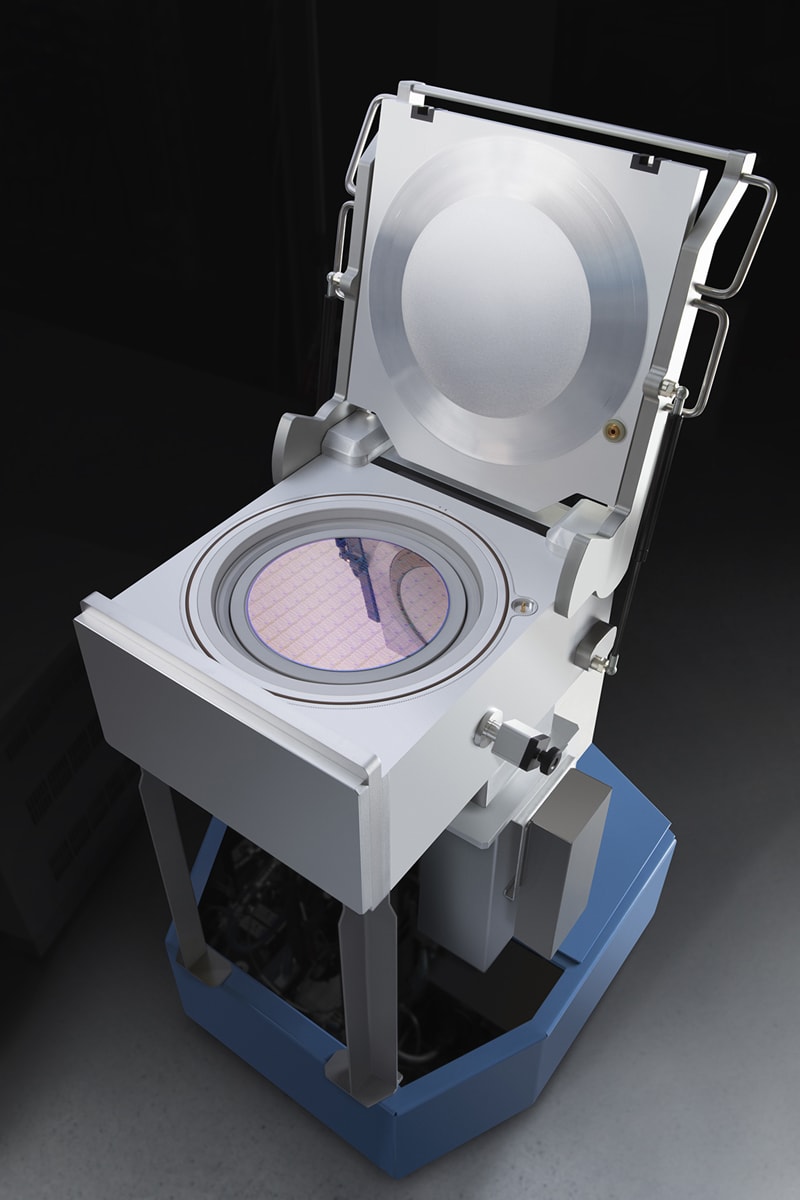

Centura iSprint SSW ALD/CVD

낮은 저항과 최소한의 일렉트로마이그레이션을 특징으로 하는 텅스텐은 로직 및 메모리 소자에서 트랜지스터를 집적 회로의 나머지 부분과 연결하는 컨택과 중간 라인(최저 레벨) 인터커넥트를 충진하기 위한 재료로 오랫동안 사용되어 왔습니다. 이전의 나노급에서는 크기가 더 컸기 때문에 정합 CVD 증착을 사용해 텅스텐 충진 집적화가 가능했습니다. 하지만 오늘날의 첨단 나노급에서는 소형화와 리엔트런트 프로파일 때문에 이러한 방법을 사용해 이러한 형상에서 완전하고 빈틈 없는 텅스텐 충진을 구현하기가 점점 더 어려워지고 있습니다. 초소형 개구부의 상단부 주변에 돌출부가 있으면 정합 공정 중에 공극 없이 형상을 완전하게 충진하는 것이 불가능합니다. 공극이 없더라도 정합 증착의 결과로 불가피하게 중앙에 빈틈이 생기게 됩니다. 이러한 특성으로 인해 매우 작은 형상은 CMP 중에 추가적인 결함이 발생할 위험이 높습니다. 첨단 칩 설계에서는 형상 밀도가 높고 불필요한 비아 중복이 없기 때문에 단 하나의 공극이 있더라도 소자 고장과 수율 저하가 발생할 수 있습니다.

Centura™ iSprint™ ALD/CVD SSW 시스템은 어플라이드 머티어리얼즈가 컨택 응용 분야를 위한 재료 기술과 금속 CVD 분야에서 오랫동안 쌓은 전문 지식을 활용해 고유한 "선택적" 증착 억제 원리를 채택하여 빈틈 또는 공극이 없는 상향식 충진을 구현합니다. 충진 품질이 향상되면 텅스텐 체적이 증가하고(저항감소 가능), 더욱 견고한 형상을 만들 수 있으며, 유전체와 식각 오픈 단계에 대한 요건을 완화해 성능, 소자 설계, 수율을 개선시킬 수 있습니다.

자세한 내용을 보려면 여기를 클릭하세요.

Centura iSprint SSW ALD/CVD 공정은 고유한 “선택적” 증착 억제 원리를 채택하여 업계 최초로 공극과 빈틈이 없는 상향식 CVD W 갭 충진을 구현합니다. 또한 W 체적을 최적화해서 더욱 견고한 형상을 만들고 수율 향상을 지원합니다.