半導體 (Semiconductor)

Endura® Volta® W CVD

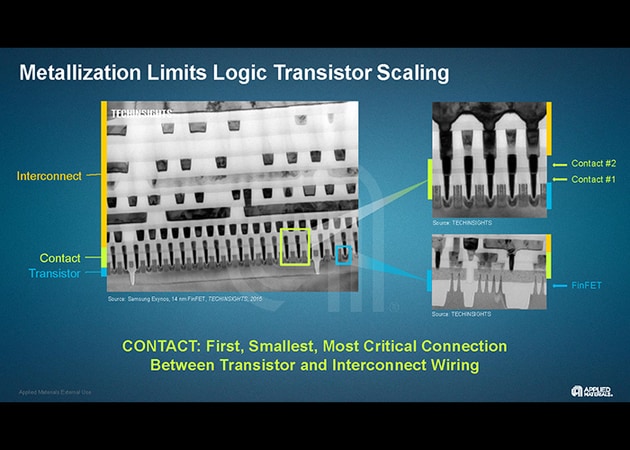

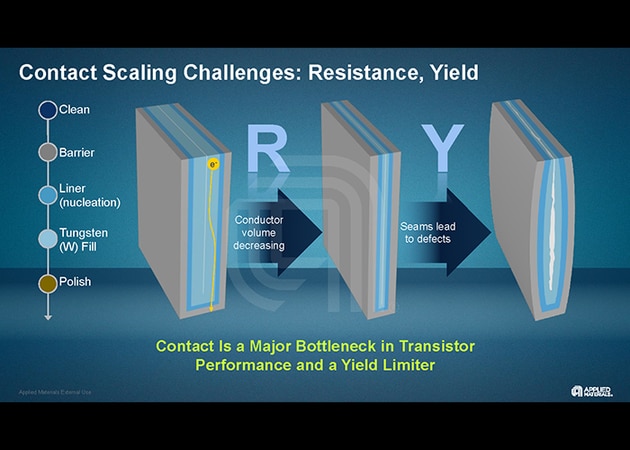

鎢具備低電阻係數、大量均勻填充的特性,廣泛用於邏輯接觸點、中段和金屬閘極填充應用。接觸點和局部導電層構成了電晶體與其餘電路之間的關鍵電子通路。因此,低電阻率對於確保穩健可靠的元件性能至關重要。然而,隨著節點不斷微縮,導電層尺寸逐漸縮小,使得接觸點電阻成為實現最佳電晶體性能的一個障礙。

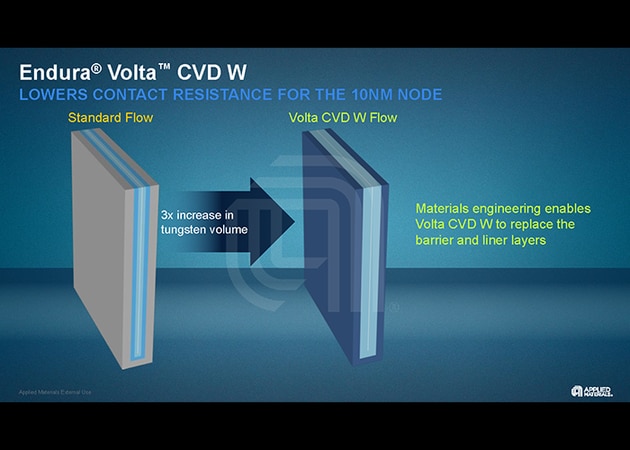

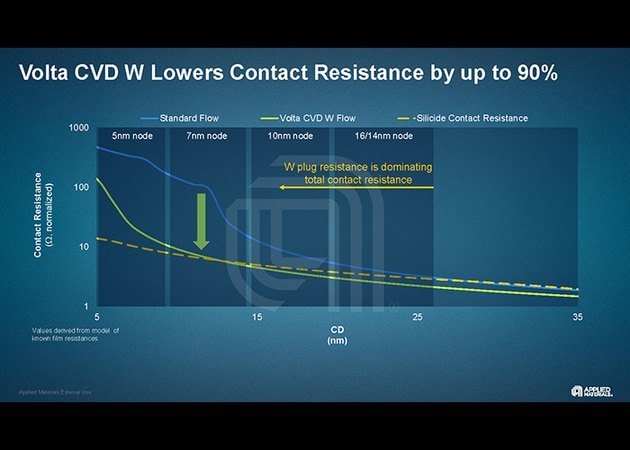

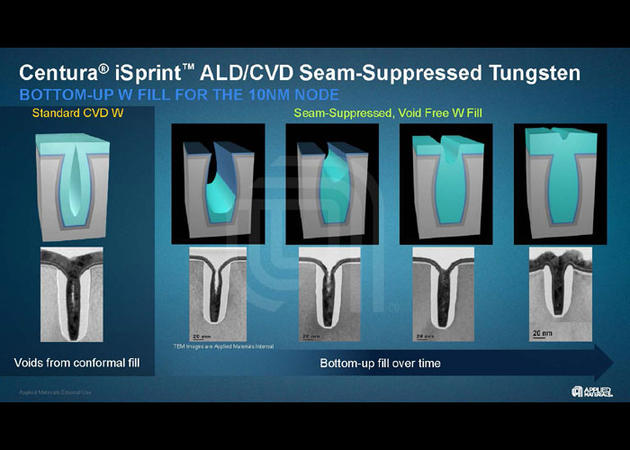

隨著導電層橫截面繼續縮減,越來越多的體積被金屬阻障層和成核層佔據,為導電金屬填充所留的體積變小。此外,插塞中每添加一層金屬介面,都會使接觸點電阻問題更加惡化。Volta CVD W 系統透過增強反應室硬體,使系統能以專業化學物沉積 W 鎢碳薄膜,並藉此緩解這些負面效應。這種獨特材料既能充當襯墊層,也能用作成核層。此材料可以堅固地粘結到介電質,阻止後續大量沉積製程帶來的氟擴散效應;其電阻率比一般襯墊層 (如 TiN) 低 70%。此外,薄膜成分主要為鎢 (W),因此可作為大量鎢薄膜的成核基板。介面薄膜的總厚度更薄,因此能加大可用於低電阻率鎢填充的體積。

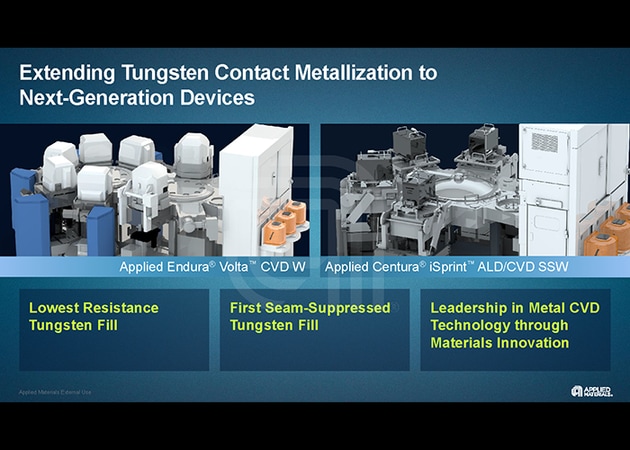

Volta CVD W 薄膜最高可將接觸點電阻降低 90%,實際情形取決於臨界線寬和製程流程。因此,此薄膜能改善元件功率傳輸、性能和效能,並可將鎢中段導電層插塞擴展用於下一代元件。更低的電阻也可在特定節點達到更大幅的微縮,實現更高元件密度。

點選此處了解更多資訊。

- 1 / 7

- 2 / 7

- 3 / 7

- 4 / 7

- 5 / 7

- 6 / 7

- 7 / 7