半導體 (Semiconductor)

解決方案與軟體

圖形成像控制

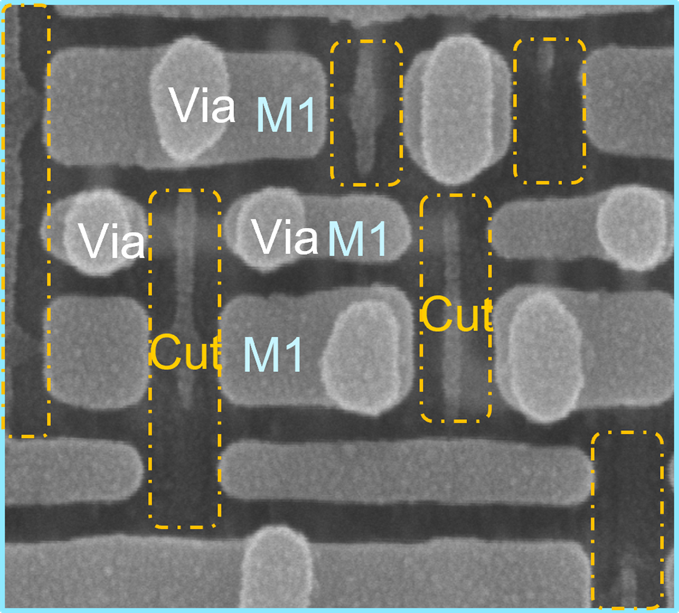

圖形成像控制是一連串關鍵的量測步驟,確保在晶圓上創建並成形出正確的材料尺寸、位置與組合。

由於現今元件架構複雜,若沒有內嵌式量測技術對實際臨界線寬大小和位置進行測量並提供反饋,並確保新結構與先前製程步驟的結構能完全對位,便無法進一步創建電晶體和導線。

應用範圍從開發初期對於製程容許範圍的開發和驗證,以至於內嵌臨界線寬、晶圓面均勻度、熱點特性和疊對測量等高採樣。 透過這些應用,元件製造商得以加速上市時間,確保良率水準,並在製造過程的早期階段取得元件效能與可靠性的可預測性。