半導體 (Semiconductor)

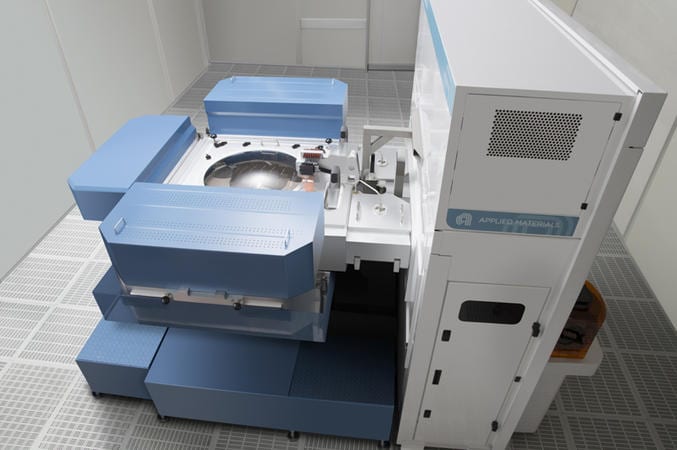

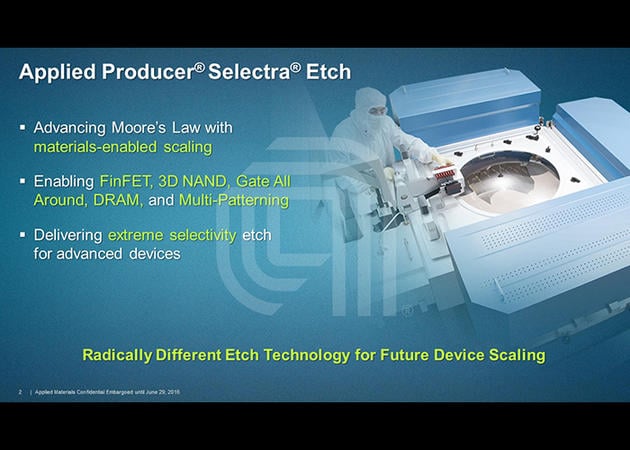

Producer® Selectra® Etch

Producer Selectra Etch 系統推出前所未有的功能特性,透過進一步微縮三維邏輯和記憶體尺寸,來維持摩爾定律的動力。此製程可針對一個或多個薄膜的選擇比來除去特定材料。

在建立先進積體電路中,晶片線寬尺寸逐漸變小,深寬比變得更高,封裝也越來越密集。元件圖案化或清潔是否夠精密,將大大影響元件最後的可靠性和效能。選擇性不足所造成的材料去除不全和臨界線寬加大,對元件效能和良率有不利影響。高深寬比線寬的圖案變形 (線路彎曲和圖案損壞) 也可能影響下一代元件的良率。

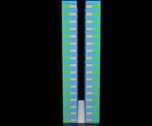

Selectra 系統解決了所有這些問題。此系統獨特的製程能夠實現先進 FinFET 的原子級蝕刻控制、均勻一致的三維 NAND 凹槽和高深寬比 DRAM 結構的無損清潔。

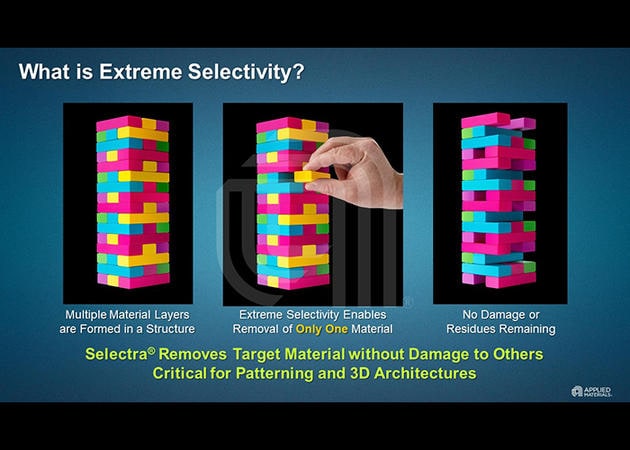

該系統採用自由基化合物來提供可調選擇性,能夠以原子級精密度去除各種介電質、金屬和半導體薄膜。這項技術可擴展今日 FinFET 元件的運用範圍,並可促進未來環繞式閘極結構,是推動摩爾定律的關鍵因素。

傳統製程的選擇性不足,會導致 NAND 堆疊層頂部附近的鎢凹陷大於底部,造成元件效能降低。

材料選擇性不足會導致濕式蝕刻化學品將圓柱形 DRAM 電容中的所有薄層擴大,造成不必要的直徑擴張。

與晶面結構強相關的濕式蝕刻製程,會導致多晶矽殘留於先進邏輯電晶體的狹小空間中。

濕式蝕刻後在乾燥步驟期間會產生毛細作用力 (「靜摩擦力」),並導致高深寬比之結構倒塌。

Selectra 製程的鎢選擇性可經過調整,在整個三維 NAND 堆疊層上形成極其均勻的蝕刻凹槽。

Selectra 製程可經調整,只針對必須增加圓柱體直徑的薄層進行選擇性的蝕刻。

Selectra 製程可去除所有多晶矽殘留,提供潔淨無污染的絕緣層,以供後續之金屬閘極沉積。

Selectra 全乾式製程可保持脆弱結構的完整性。

- 1 / 5

- 2 / 5

- 3 / 5

- 4 / 5

- 5 / 5