半導體 (Semiconductor)

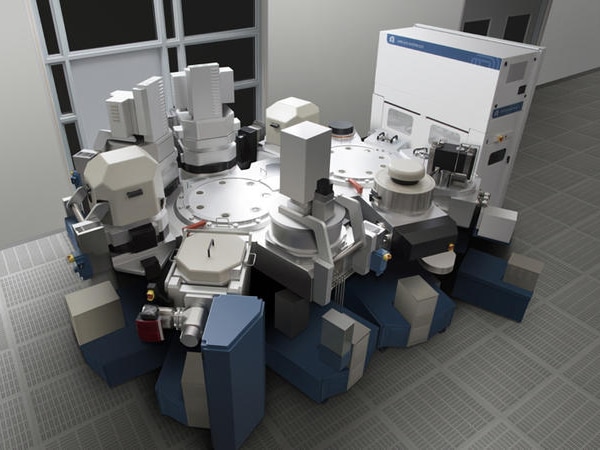

Endura® Versa™ XLR2 W PVD

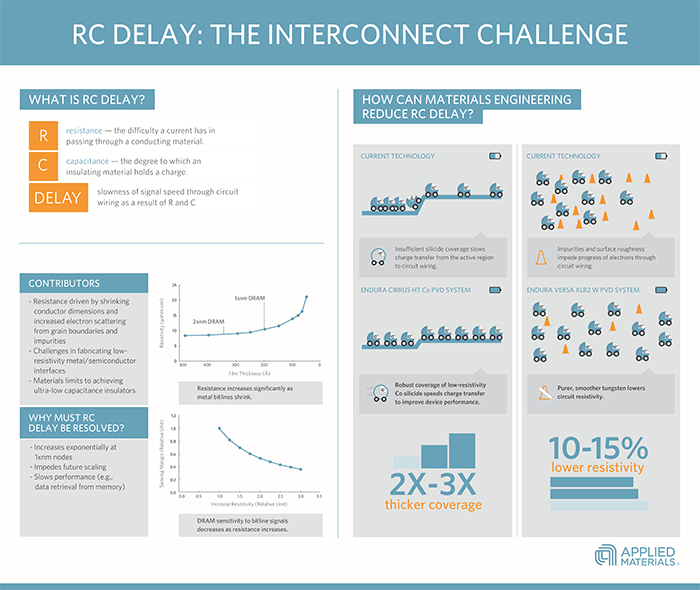

隨著積體電路及其組件持續向下微縮,組件之間的金屬導線和接觸點的尺寸也在縮小。這種趨勢造成這些連接組件的電阻越來越高。為生產更精小、更快速的電子元件,連接組件必須維持最小電阻,元件才可能進一步微縮。

這種較高電阻所造成的慢化效應通常稱作阻容延遲 (即 RC 延遲),並以多種方式影響著電路。除這種不良效應以外,RC 延遲還會降低通過位元線從 DRAM 結構讀寫數據的速度。此外,更高的電阻還會產生更高的功耗,會對行動技術產生不良副作用。

降低線路電阻的最簡單方法是增加導電金屬的體積,就是使用更寬、更高的導線。但是,導線寬度增加會限制元件微縮,導線高度增加會增大電容,造成更大的蝕刻難度。因此,降低先進元件的接線電阻著重在改善導電材料 (DRAM 位元線採用的鎢 W 材料) 的屬性。

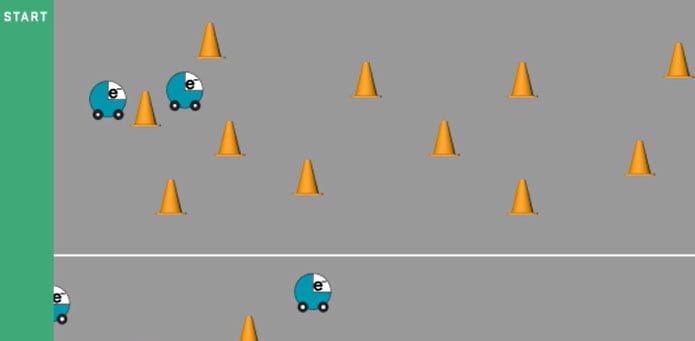

導體電阻是電子在穿過導體時遇到散射點的密度函數。薄膜中的雜質、晶粒邊界和表面粗糙度是減緩電子移動速度的一些障礙。Versa XLR2 W PVD 反應室通過沉積更純淨、更光滑的鎢膜來降低導電層電阻,其電阻率比使用當前技術所沉積的鎢的電阻率低 10-15%。

新系統以關鍵硬體組件的創新方式來達到品質的提升,如磁電管來源、新穎的製程化學和電漿特性調整。Versa XLR2 W 系統可產生電阻率更低的鎢膜,將 DRAM 技術中鎢作為位元線金屬的應用推進到 1x 倍奈米節點,從而推動技術節點繼續微縮。以下動畫說明該系統產生的出色薄膜如何提升元件性能。

RC 延遲效應相當重要,因為此效應可能會成為邏輯和記憶體元件繼續向下微縮的重大障礙。對今日多功能、行動消費電子設備的性能發展來說,邏輯和記憶體元件有很大關係。

邏輯和記憶體晶片中的主動元件 (電晶體) 均通過金屬接線,進行元件間或元件與晶片其他區域的電子連接。這些接線是以不導電 (絕緣) 介電層相互隔離。在邏輯和記憶體晶片中,導電層的作用是將訊號從晶片一個區域傳輸到另一個區域。以最快速度完成訊號傳輸,同時在縮小幾何結構過程中將訊號損失降至最少,這一點對元件微縮極為重要。在邏輯元件中,微縮是指面積縮小,也就是採用創新材料和設計,在更小的面積中封裝越來越多的電路。在價格影響很大的 DRAM 製造業中,成本必須嚴格管控;因此,微縮會著重在從目前材料和設計中取得越來越強的性能。一般來說,邏輯和記憶體接線中的訊號傳遞速度取決於相同的基本原理和阻容 (電阻和電容,RC) 值。最理想是能同時降低電阻和電容。但對記憶體製造商而言,開發電容較低的絕緣材料並將其積成在製造流程中的成本特別高。因此,降低電阻成為保證微縮性能的首選方法。目前有不同的解決方案可解決 RC 難題,採取哪種方案取決於電荷是垂直穿過不同的佈線層,還是沿導體橫向通過。不過,無論是哪種情況,目標都是要將低金屬接線電阻降至最低。在垂直尺寸上,解決方案旨在將介面電阻率降至最低。電氣接觸點會將元件的主動區連接到第一層金屬接線層。半導體至金屬介面 (或歐姆接觸) 形成了主動區與金屬接觸點之間的接面。目的是確保電荷能夠從主動區通過接觸點傳到上層接線層,然後返回。為了在歐姆接觸之間達到快速的最大電荷傳輸,低電阻率材料因應而生。為達到這個目的,業界已採用低電阻矽化鈷為標準;這種材料有效性取決於是否能沉積均勻的矽化鈷層,並形成穩定的歐姆接觸。參閱 ENDURA CIRRUS HT Co PVD。