-

ALD

-

CMP

-

CVD(化学气相沉积)

-

ECD

-

外延生长

-

刻蚀

-

离子注入

-

测量与检测

-

Pattern Shaping

-

光掩膜

-

PVD(物理气相沉积)

-

快速热处理(RTP)

-

模拟

-

化合物半导体

-

微机电系统(MEMS)

-

功率

Endura™ Versa™ XLR2 W PVD

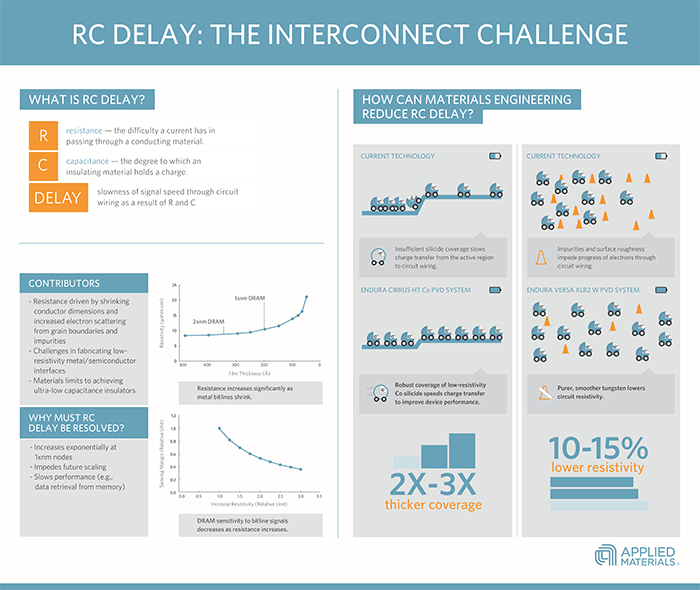

随着集成电路及其组件继续微缩,组件之间的金属互联线和接触件的尺寸也在缩小。其中一个结果为,这些连接器中的电阻越来越高。为生产更紧凑、更快速的电子器件,必须最大限度地降低电阻,以便能够进一步地微缩。

这种更高的电阻所造成的慢化效应通常被称做阻容延迟(或 RC 延迟),并以多种方式影响着电路。除这种不良效应以外,RC 延迟还会降低通过位线从 DRAM 结构读写数据的速度。此外,更高的电阻还会引起更高的功耗,这会为移动技术带来不良的副作用。

降低线电阻的最简单方法是增加导电金属的体积,即使导线更宽和更高。但是,更宽的导线会限制微缩,更高的导线会增加电容,并带来更大的刻蚀挑战。因此,降低尖端器件的导线电阻侧重于提升导电材料(DRAM 位线采用钨 (W))的性能。

导体电阻是电子在穿过导体时所遇散射点密度的函数。薄膜中的杂质、晶粒边界和表面粗糙度是减缓电子移动速度的某些障碍。Versa XLR2 W PVD 腔通过沉积更纯净和更光滑的钨膜来降低互联电阻,该钨膜比使用当前技术所沉积的钨的电阻率低 10-15%。

新系统借助关键硬件组件的创新实现了这一质量增强,如微波源磁控管、新颖的工艺化学和等离子体特征调制。Versa XLR2 W 系统所生产的电阻率更低的钨是微缩的促成者,它将扩展作为位线金属的钨在用于 1xnm 节点的 DRAM 技术中的用途。以下动画解释该系统的出色薄膜如何提升器件的性能。

RC 延迟举足轻重,因为这可能成为继续向下微缩逻辑和存储器设备的重大障碍,而该项技术对于提升当前的多功能、移动消费电子设备的性能至关重要。

逻辑和存储芯片中的有源器件(晶体管)均通过金属线以电气方式连接彼此或芯片的其他区域。这些导线通过不导电(绝缘)介电层彼此分离。在逻辑和存储芯片中,互联线的作用为将信号从芯片的一个区域传输到另一个区域。能尽快完成信号传输,并能最大限度地降低几何尺寸缩小所造成的信号损失,这一点对器件微缩至关重要。在逻辑芯片中,微缩是指面积缩小,即借助于材料和设计创新,在更小的面积中封装越来越多的电路。在对价格敏感的 DRAM 制造领域,必须大幅控制成本,所以微缩侧重于从现有的材料和设计中获得逐步增强的性能。总之,逻辑和存储器导线中的信号传输速度受相同的基本原理支配,并取决于电阻和电容 (RC) 的乘积。同时降低电阻和电容是理想的方法。但是,对于存储器制造商而言,开发电容较低的绝缘材料并将其集成到制造流中的成本特别高。因此,降低电阻成为保证微缩后的性能的首选方法。根据电荷是垂直穿过不同的布线层,还是沿导体的长度横向通过,需要使用各种解决方案来应对 RC 挑战。尽管,无论对于哪种情况,其目标都在于最大限度地降低金属线的电阻。在垂直尺寸中,解决方案旨在最大限度地减小界面电阻。电接触件将有源区连接到第一级金属布线层。半导体-金属界面(或欧姆接触层)形成了有源区和金属接触层之间的接面。其目标在于,确保电荷能够从有源区通过接触件前往上层布线层,然后返回。为在欧姆接触层之间实现最快速和最大化的电荷传输,应形成低电阻率材料层。低电阻率硅化钴已作为此用途的行业标准被采用,其有效性依赖于能否沉积均匀的一层,以形成坚固的欧姆接触层。参见 ENDURA CIRRUS HT Co PVD。