半導體 (Semiconductor)

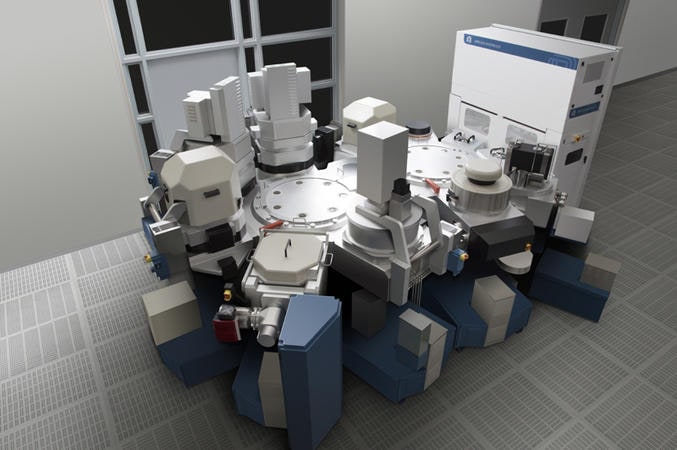

Endura® Cirrus™ HT Co PVD

微縮還有另一個副作用,就是深寬比隨著先進電路中線寬密度的增加而增加。因此,要沉積出具備足夠底部覆蓋率的薄膜變得越來越困難,最終元件也無法達到適當的電氣性能。在 DRAM 結構中,主動區與第一層金屬導電層之間的半導體至金屬介面特別重要。為在這些介面之間達到快速的最大電荷傳輸,應使用低電阻率材料 (矽化鈷);其有效性取決於是否可沉積適當厚度的均勻介面層。

Endura Cirrus HT Co PVD 系統可通過增強功能來達到所需的矽化物覆蓋率;這些功能能克服接觸點面積不斷縮小和深寬比不斷增加所帶來的挑戰。該系統使用高頻 RF 源來產生電漿,與其他可能的來源技術比較,電漿的金屬離子濃度更高,因此能夠在高深寬比特徵的底部達到出色的覆蓋厚度和均勻度。晶圓的負電壓會將正金屬離子引入窄孔中;由於有更多的金屬離子,所以對高深寬比接觸孔點底部的覆蓋度比當前技術所達到的覆蓋度厚兩倍或三倍。因此,製程中可形成堅固的矽化鈷層,能夠減少電荷在金屬與半導體之間的傳輸障礙。

該系統將 Siconi 矽化前預清潔與用於 DRAM 外圍電路中的直接接觸點應用的 PVD 鈷和氮化鈦蓋帽沉積結合在一起。

歐姆接觸帶來的挑戰

在記憶體元件中,歐姆接觸 (導體至金屬介面) 將主動區與金屬接線層連接在一起。隨著記憶體元件不斷微縮,一代代節點的歐姆接觸面積縮小了約 70%,而線寬深寬比增加了;線寬內部必須沉積低電阻矽化物,才可形成這類接觸點。在 1xnm DRAM 中,這兩個因素使得形成足夠厚的矽化鈷層日益困難,有足夠的厚度才能確保電荷快速、可靠地從主動區通過接觸點傳到上層接線層,然後返回。

以下動畫說明了歐姆接觸的概念以及 Endura Cirrus HT Co PVD 系統所產生的厚矽化物覆蓋對元件性能的有利影響。

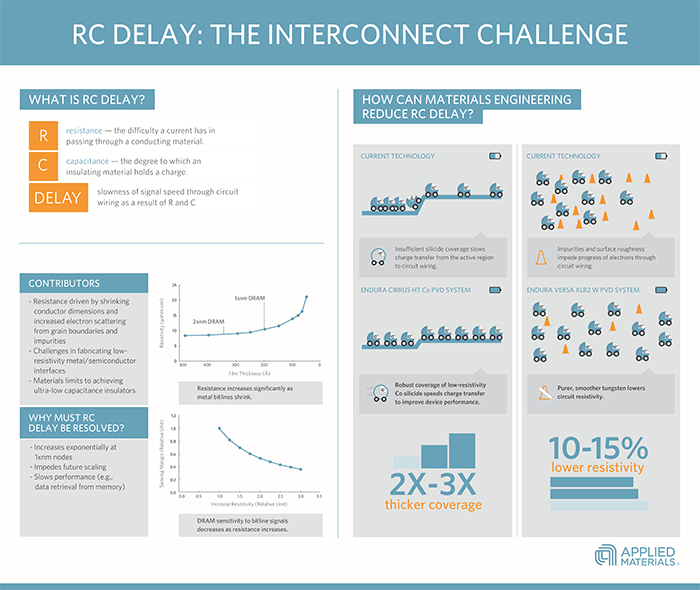

RC 延遲效應相當重要,因為此效應可能會成為邏輯和記憶體元件繼續向下微縮的重大障礙。對今日多功能、行動消費電子設備的性能發展來說,邏輯和記憶體元件有很大關係。

邏輯和記憶體晶片中的主動元件 (電晶體) 均通過金屬接線,進行元件間或元件與晶片其他區域的電子連接。這些接線是以不導電 (絕緣) 介電層相互隔離。在邏輯和記憶體晶片中,導電層的作用是將訊號從晶片一個區域傳輸到另一個區域。以最快速度完成訊號傳輸,同時在縮小幾何結構過程中將訊號損失降至最少,這一點對元件微縮極為重要。在邏輯元件中,微縮是指面積縮小,也就是採用創新材料和設計,在更小的面積中封裝越來越多的電路。在價格影響很大的 DRAM 製造業中,成本必須嚴格管控;因此,微縮會著重在從目前材料和設計中取得越來越強的性能。一般來說,邏輯和記憶體接線中的訊號傳遞速度取決於相同的基本原理和阻容 (電阻和電容,RC) 值。最理想是能同時降低電阻和電容。但對記憶體製造商而言,開發電容較低的絕緣材料並將其積成在製造流程中的成本特別高。因此,降低電阻成為保證微縮性能的首選方法。目前有不同的解決方案可解決 RC 難題,採取哪種方案取決於電荷是垂直穿過不同的佈線層,還是沿導體橫向通過。不過,無論是哪種情況,目標都是要將低金屬接線電阻降至最低。在垂直尺寸上,解決方案旨在將介面電阻率降至最低。電氣接觸點會將元件的主動區連接到第一層金屬接線層。半導體至金屬介面 (或歐姆接觸) 形成了主動區與金屬接觸點之間的接面。目的是確保電荷能夠從主動區通過接觸點傳到上層接線層,然後返回。為了在歐姆接觸之間達到快速的最大電荷傳輸,低電阻率材料因應而生。為達到這個目的,業界已採用低電阻矽化鈷為標準;這種材料有效性取決於是否能沉積均勻的矽化鈷層,並形成穩定的歐姆接觸。在橫向尺寸上,解決方案旨在使形成接線的金屬導電性達到最佳化。故名思義,線路電阻是指接線尺寸 (寬、高、長) 與製造接線所用材料 (通常為鎢或銅) 的特定屬性等兩者的函數。降低線路電阻的最簡單方法是增加導電金屬的體積,就是使用更寬、更高的導線。但是,導線寬度增加會限制元件微縮,導線高度增加會增大電容,造成更大的蝕刻難度。因此,降低先進元件的接線電阻著重在改善導電材料的屬性。請參閱 ENDURA® Versa™ XLR2 W PVD。