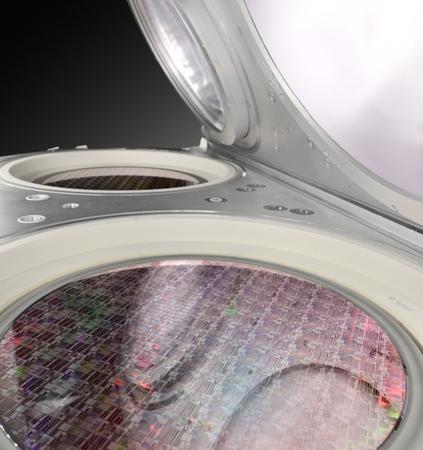

Producer® Onyx®

- 1 / 4

- 2 / 4

- 3 / 4

- 4 / 4

- 革新的な膜処理により、携帯機器の電池寿命の延長を可能にする

チップ配線の絶縁性が向上します。 - ロジックチップを22nm以降のノードにスケーリングするために、Low-k技術を発展させます。

- パッケージングの歩留まり改善のため、チップの機械的強度を向上します。

集積回路では、導電性銅配線は絶縁(非導電性)材料で絶縁されています。半導体デバイスの小型化が進むに連れ、デバイス速度の向上は絶縁材料の誘電率(k)に著しく影響されるため、誘電率も共に低下させる必要があります。チップメーカーは、絶縁膜のk値 を二酸化シリコン材料の4.0から段階的に減少させ、180nmではフッ素の添加によって3.5まで、90/65nmでは炭素を導入することで3.0に、45/32nmでは多孔質を導入することで2.5まで低減しました。多孔性Low-k誘電体は現在、銅配線2xnmテクノロジーノードにおいて、要求されるキャパシタンスの低減を達成するためには、極めて低い(k~2.2)k値のLow-k材料が必要となります。

これらのLow-k 材料は、10〜12のメタル層構造の製造において150以上の工程にさらされた後、パッケージングと組立工程における負荷にも耐えなければなりません。プラズマエッチング、フォトレジストアッシング、ウェット洗浄、化学機械研磨(CMP)、バリア成膜前の酸化銅の除去は、Low-k膜の表面層の化学構造を壊す可能性があります。

Applied Producer Onyxは、 Low-k膜の化学的完全性と強度を回復する処理を施す、斬新なプロセスです。Onyxプロセスは膜の表面だけでなく膜全体を処理します。このため、 応力や硬度といった構造的に重要な特性を高めつつ、総合的に最低のk値が得ることができます。

Producer Onyxでは、この処理の結果として得られた Low-k 誘電体が、ローカル配線の形成に必要な2xnmの要件を満たすと共に、後の先進パッケージング工程にも確実に対応できるようにします。さらに、歩留まり低下の要因となる影響を抑制することで、他のプロセス(エッチングなど)の生産性も高めます。

同プラットフォームは革新的なTwin Chamber®構造により、最大6枚のウェーハの同時処理が可能で、生産性が向上します。