DRAM 구조

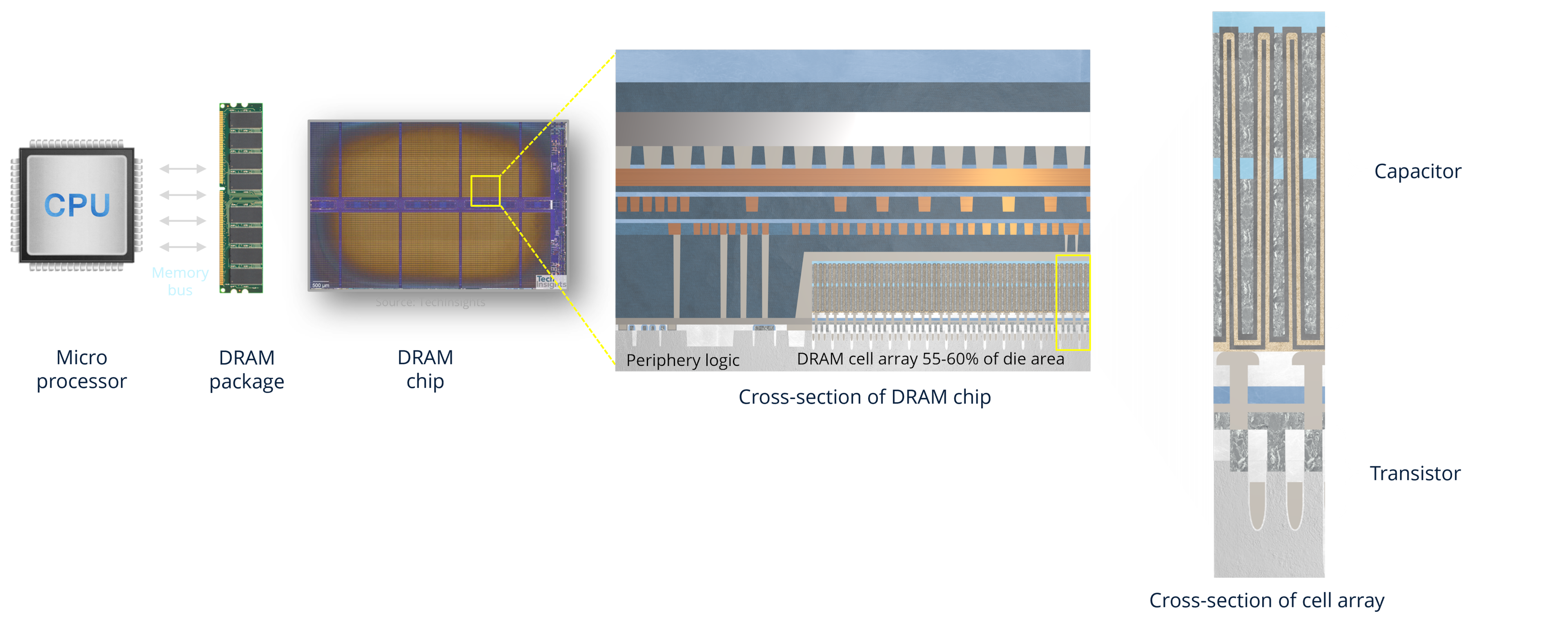

동적 임의 접근 기억 장치(DRAM) 컴퓨터의 주요 구성 요소이며 프로세서가 매초 수행하는 수십억 번의 연산을 하는 데 필요한 정보를 빠르게 저장하는 곳입니다. 일반적인 DRAM 칩에는 다음과 같은 세 가지 주요 영역이 있습니다:

- 작은 커패시터에 개별 비트가 저장되는 셀 어레이;

- 감지 증폭기 및 워드 라인 디코더와 같은 소자가 셀 어레이의 데이터 접근 방식을 결정하는 로직 또는 코어 영역;

- DRAM 칩 입출력을 위한 통신 링크가 형성된 주변부입니다

이러한 세 가지 영역 모두 업계에서 계속 증가하는 DRAM 성능 요구 사항을 충족할 수 있도록 미세화를 거쳐야 합니다. 해당 미세화에 대한 당면 과제는 커패시터 내 저장할 수 있는 전하의 최대화, 감지 증폭기 변동성의 축소, 회로망 배선으로 인한 전력 손실 축소로 요약될 수 있습니다.

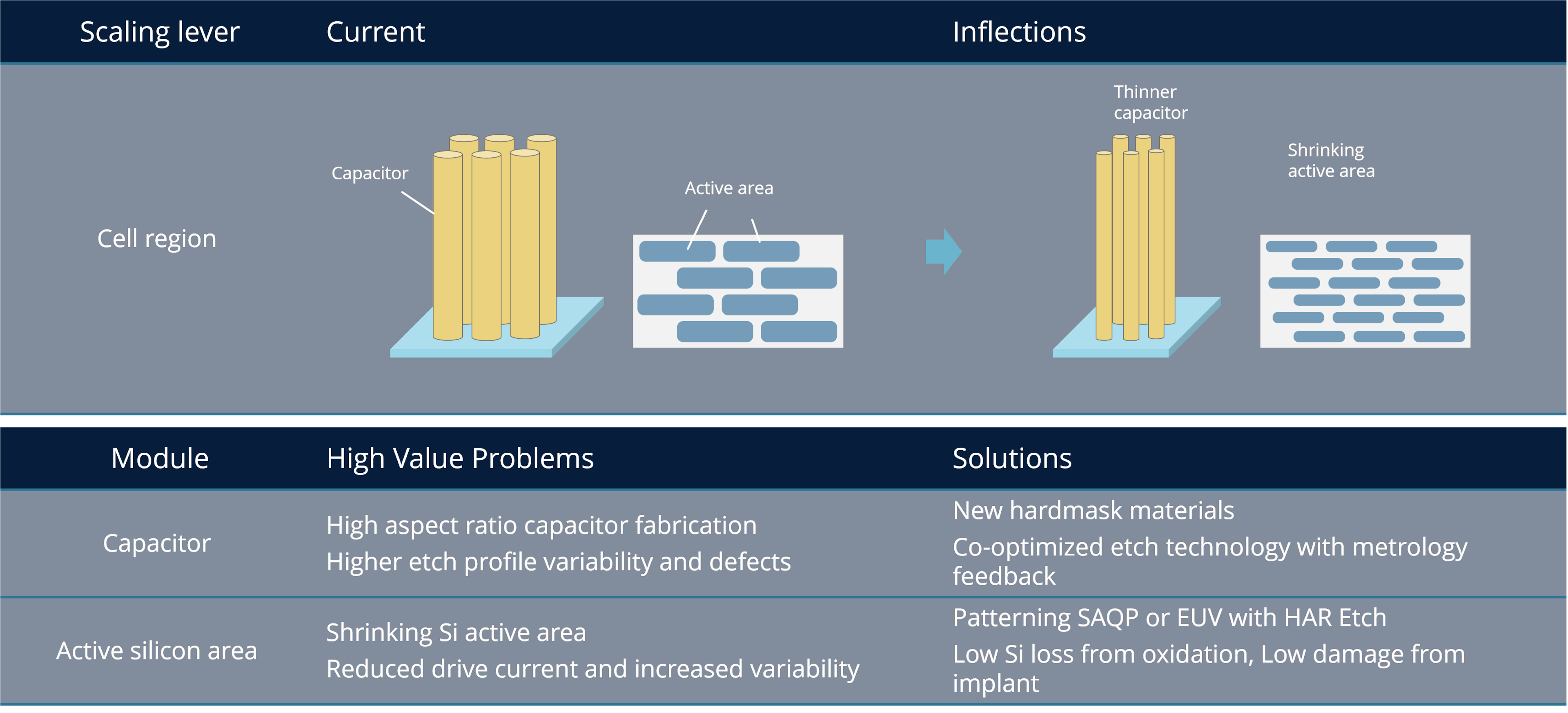

셀 어레이 미세화

데이터가 저장되는 DRAM 셀 어레이는 다이에서 가장 큰 부분입니다. 다이의 밀도는 단위 면적당 셀의 개수를 늘려 증가시킬 수 있습니다. 이를 위해서는 셀 커패시터 및 트랜지스터의 치수를 줄여야 합니다. 이는 게이트 및 비트라인의 피치 감소 외에도 DRAM 셀의 미세화에 도움이 됩니다.

당사의 첨단 DRACO™ 하드마스크 및 Sym3™ 하드마스크 식각 장비를 이용한 고유 조합을 통해 고객은 커패시터 식각에 사용되는 하드마스크에서 30% 줄어든 두께를 달성할 수 있었습니다. 게다가, 커패시터 홀 직경의 변동성을 50% 줄일 수 있었습니다. 이는 브리지 결함을 100배 이상 줄이는 데 도움이 되었습니다.

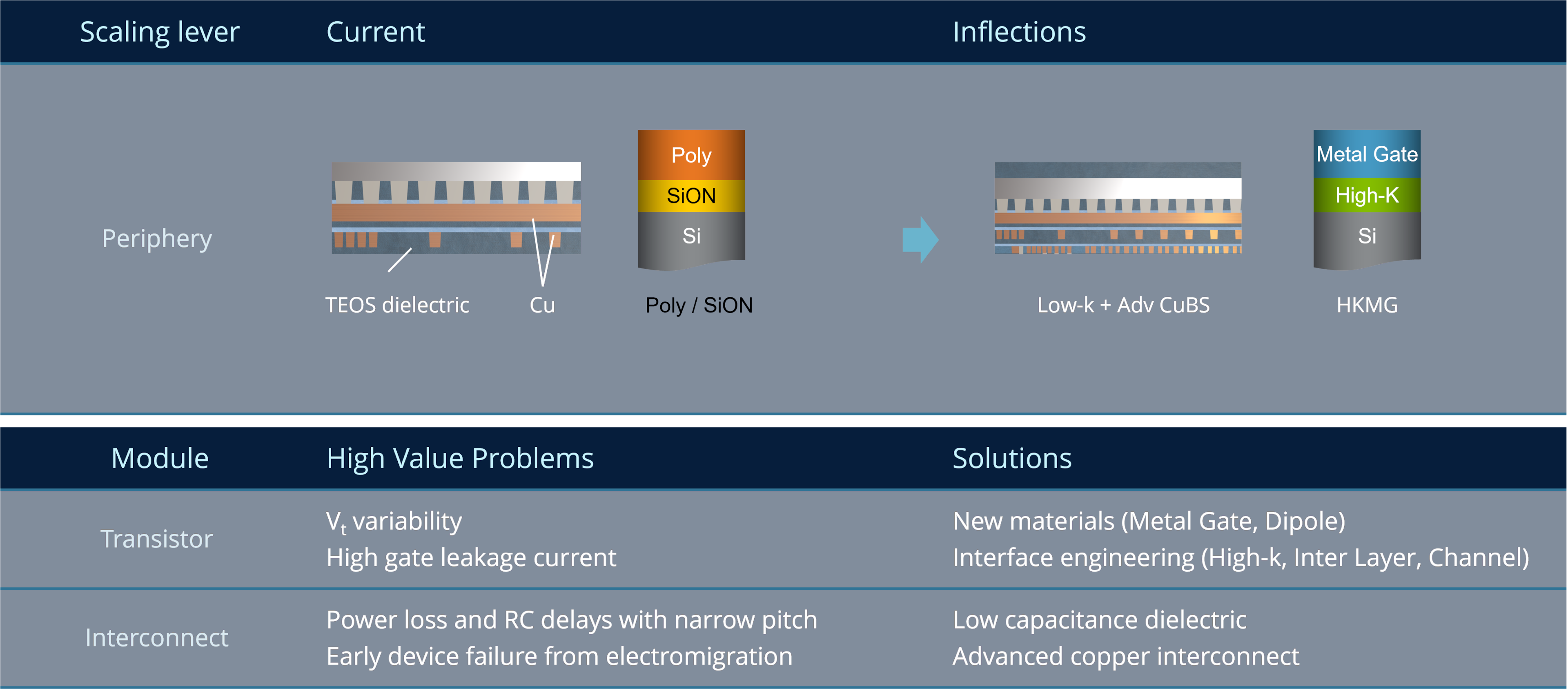

주변부 로직 미세화

DRAM 셀 데이터는 주변부 로직 소자에 의해 관리됩니다. 주변부 회로는 주로 고속 로직 트랜지스터 및 DRAM의 다양한 부분을 연결하는 배선으로 구성됩니다. DRAM 셀에 저장된 정보의 무결성을 유지하기 위해서는 이 회로에 대한 신호를 최대화하는 것이 매우 중요합니다.

DRAM 제조업체는 트랜지스터 성능을 향상시키기 위해 PolySiON 유전체를 High-K 재료로, 폴리실리콘 게이트를 금속 게이트로 교체하고 있습니다. 서로 다른 여러 막이 각각의 위로 증착될 때 계면 및 막의 결함은 전자 수송 방식에 큰 역할을 합니다.

어플라이드 머티어리얼즈는 DRAM 후공정 구리 배선을 위해 Black Diamond™라는 업계 최고의 Low-K 유전체 제품을 제공합니다. Black Diamond는 유전율을 25% 줄일 수 있습니다. CVD 코발트와 함께 당사의 Endura CuBS 제품 채택으로 인해 후공정 구리 금속 배선 공정의 신뢰도는 10배 넘게 향상되었습니다.

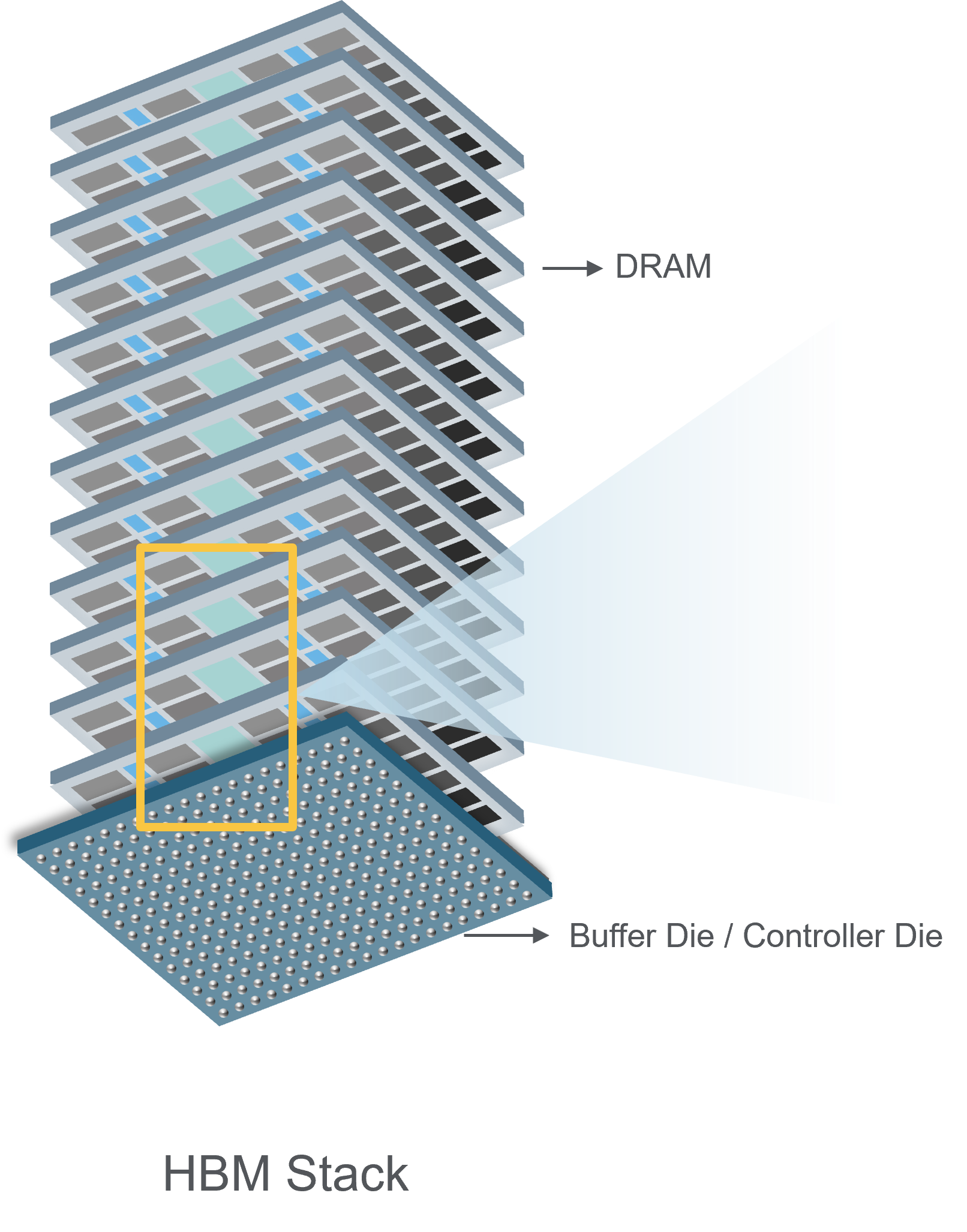

DRAM 스태킹 - HBM

AI 애플리케이션에 필요한 방대한 양의 메모리를 제공하기 위해 칩 제조업체는 고급 DRAM 적층으로 구축된 고성능, 저지연 아키텍처인 고대역폭 메모리(HBM)로 전환했습니다. DRAM 칩의 혁신도 중요하지만, HBM의 밀도와 대역폭은 첨단 3D 패키징을 통해 실현됩니다. 어플라이드 머티어리얼즈는 업계의 HBM 도입 확대를 지원하는 데 필요한 재료 공학 기술 분야의 선도 기업입니다. 자세한 내용.

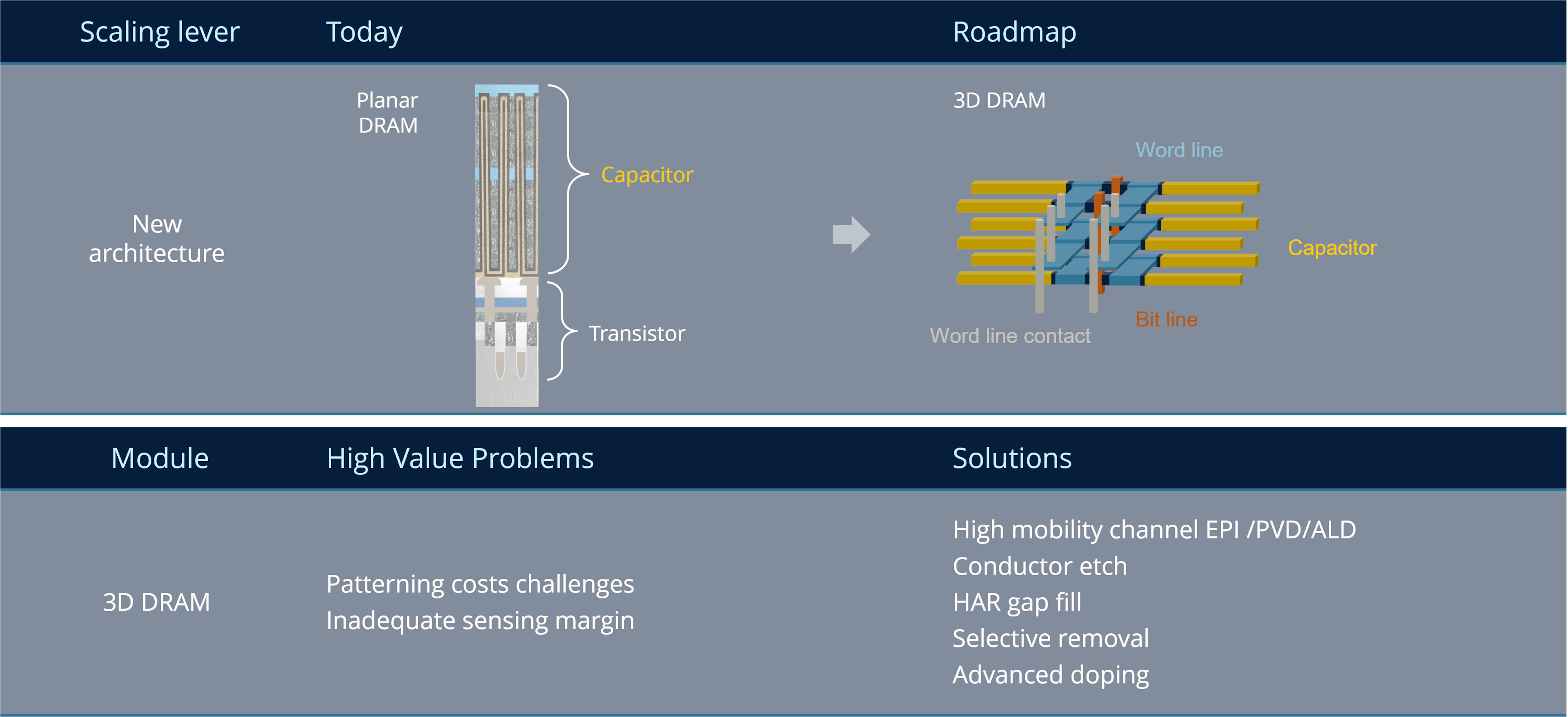

수직 미세화 – 3차원 DRAM

3차원 DRAM은 3차원 수직 구조 낸드와 유사하게 비트를 구조적으로 수직 방향으로 저장하는 것을 의미합니다. 하지만 DRAM은 낸드보다 거의 1,000배 더 빠르고 이동도가 높은 실리콘 기판을 채널 형성의 출발 물질로 사용하여 이러한 속도를 달성합니다. 또한 DRAM의 빠른 속도는 전하가 커패시터 내외부로 빠르게 움직일 수 있다는 사실에서 비롯됩니다. DRAM을 수직 방향으로 미세화해야 하는 경우 기타 재료 및 공정 혁신 외에도 높은 이동도 및 결함이 극도로 적은 채널을 구현하기 위해 새로운 재료 혁신이 필요합니다.

어플라이드 머티어리얼즈는 새로운 재료 혁신의 선두 주자이며 에피택시 성장, PVD, ALD와 같은 제품 및 분야를 통해 고이동성 재료 증착에 사용되는 몇 가지 핵심 기술의 단위 공정을 선도하고 있습니다. 이러한 막은 증착되고 나면 바닥층에 접근하기 위해 식각되어야 합니다. 3차원 DRAM에는 첨단 갭 충진, 선택적 제거 및 첨단 도핑 역량이 필요할 것으로 예상됩니다. 이러한 역량은 성공적인 솔루션을 구현하기 위해 빈틈 없이 통합되어야 합니다. 당사는 이러한 다양한 공정을 함께 최적화하기 위한 Integrated Materials Solutions™ 개발을 선도하여 3차원 DRAM이 직면하게 될 통합 당면 과제에 대한 전반적인 솔루션을 제공하는 핵심적인 존재가 될 것입니다.