半導體 (Semiconductor)

解決方案與軟體

推動 AI 時代

由於物聯網、大數據和人工智慧 (AI) 的需求,無論是晶片功耗、效能、面積、成本與上市時間 (PPACt™),都需要進行快速且大幅的改善。這項挑戰是我們產業邁向全新攻略的驅動力。為滿足這些需求,整體產業開始以一種全新的方式共同協作。我們選擇並行式創新而非系列式創新,在整個生態系統中(材料到系統,即 Materials to Systems™ 和系統到材料,即 Systems to Materials™)推動更大規模的協作,以加快交付 AI 時代所需的改良晶片。

PPACt 創新

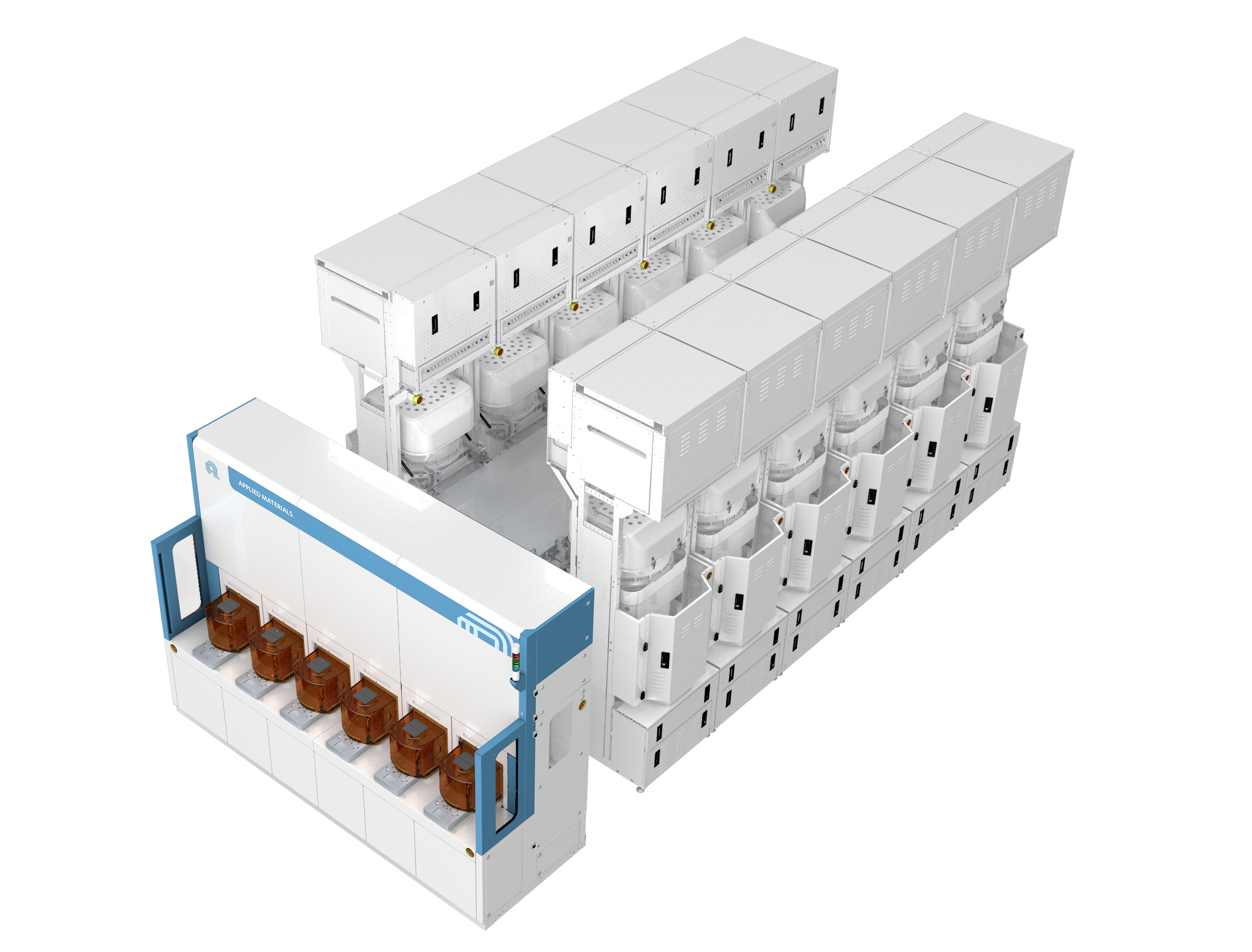

應用材料公司致力為我們的客戶與合作夥伴, 加速實現 PPACt 的全新攻略。 我們擁有最廣泛且最深入的產品組合,可將 PPACt 的創新產品推向市場。 這套產品組合針對材料和元件,以全新方式提供創建、沉積、成形、去除、改性、分析、連接的能力。 我們獨具一整套廣泛的製程技術與量測能力,且我們針對晶片與封裝,具備高度差異化實驗室的能力。 我們的 Integrated Materials Solution®(整合性材料解決方案)針對材料進行共同最佳化的沉積、去除、改性與分析,以建立新型材料並設計出全新結構,在領先技術的節點上打造高效能、低功耗的晶片。

淨零加速

我們的系統設計經久長效,可支援升級並可再利用供全新應用;同時,在零件故障或效能低於可接受標準時,還能夠輕易進行維修。 所有新生產的零件都經過精心設計以利維修,我們儘可能使用翻新零件進行維修和再製,為可持續發展和成本效益做出貢獻。 我們了解身居獨一無二的領導地位,應該對員工、客戶和社會負有重大責任,這是我們系統從一開始即注重環保設計的原因;同時,我們期盼能夠共同邁向淨零排放的倡議,創造更美好的未來。

Applied Materials Earns Intel’s 2025 EPIC Supplier Award

Accelerating Defect Inspection for More Reliable Automotive Chips

Semiconductor R&D Leaders Share Vision for Accelerating Advanced Packaging