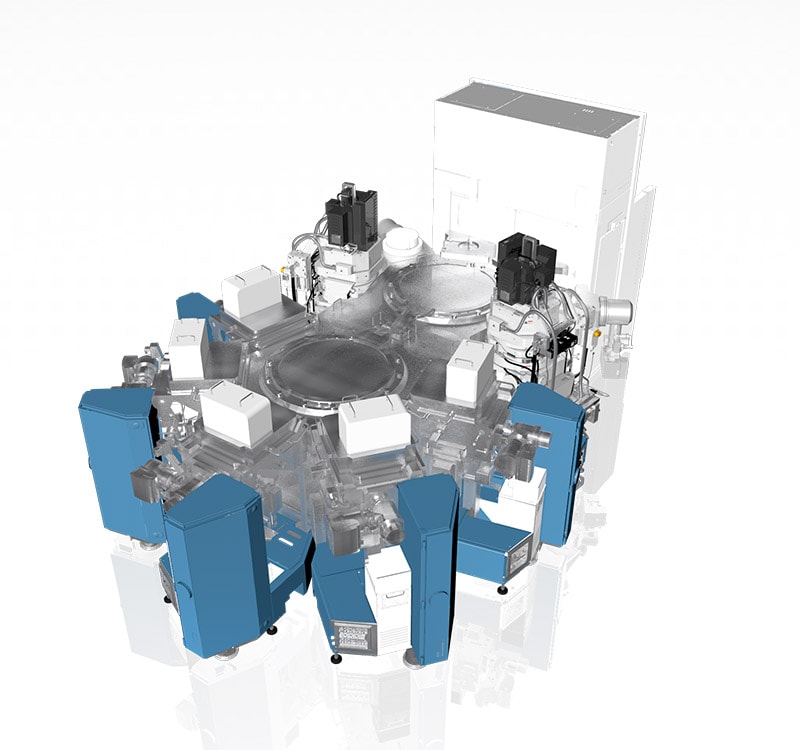

Endura® Ioniq™ W PVD

隨著積體電路及其元件持續向下微縮,元件之間的金屬導線和接觸點尺寸也在持續縮小。這種趨勢造成這些接點電阻越來越高。

這種較高電阻所造成的慢化效應一般稱作阻容延遲 (即 RC 延遲),會使速度降低並提高功耗,進而影響晶片效能。為打造更精小、更快速的電子元件,這些接點電阻必須最小化,以利實現微縮進程。

在使用 CVD 與高真空平台上預先表面處理室的開創性組合中,新型應材 Endura Ioniq 物理氣相沉積系統為 Integrated Materials Solution™,能夠在各式各樣的接觸點應用中將純鎢 (W) 金屬化。以物理氣相沉積(PVD)鎢層結合主體 (bulk)化學氣相沉積(CVD)鎢填充,取代傳統高電阻的多設備組合,包括氮化鈦襯墊層、鎢核層和鎢主體填充。Ioniq PVD反應室強化離子化與方向流量控制,使純鎢薄膜達到優異、均勻的階梯覆蓋,藉以作為低電阻的阻擋層與襯墊層。連續高真空環境可保持薄膜完整性,進一步強化金屬介面的純度與電導。

身為微縮推手,應材 Endura Ioniq PVD系統擴大鎢在 5奈米 以下的關鍵邏輯接觸點應用,同時為DRAM 與 NAND 元件之間的低電阻連接金屬化提供創新解法。