Products & Technologies

Products & Technologies

Services

Resources

Posted

June 26, 2019

Stay updated on our content.

Integrated Process Monitoring Enables New Memories

Jun 26, 2019

The Internet of Things (IoT), Big Data and Artificial Intelligence (AI) are driving the need for higher speeds and more power-efficient computing. The industry is responding by bringing new memory technologies to the marketplace. Three new types of memory in particular—MRAM (magnetic random access memory), PCRAM (phase change RAM) and ReRAM (resistive RAM)—are emerging as leading candidates for use in IoT and cloud environments.

All three of these emerging memories are based on delicate new materials that require breakthroughs in process technology and high-volume manufacturing. The critical films are so thin and variation-sensitive that metrology is crucial. The sensitivity of the deposition layers to impurities means that ideally, multiple process steps and metrology should be integrated under vacuum.

MRAM, PCRAM and ReRAM promise to enable higher system performance and lower power than many of today’s designs based on mainstream memories. Already, major semiconductor manufacturers have announced plans to commercialize MRAM and PCRAM. This means progress is being made in engineering complex new materials and depositing them with atomic precision at an industrial scale.

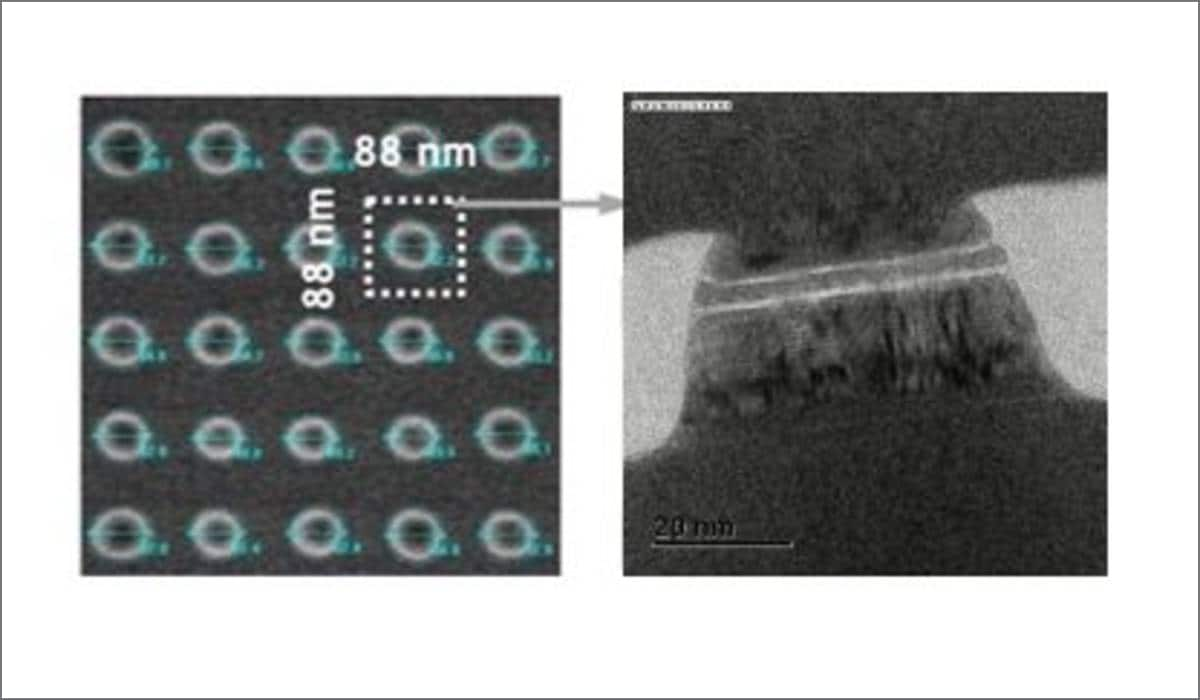

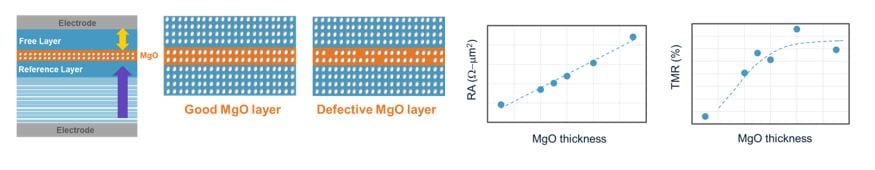

MRAM is formed by precisely depositing at least 30 different metal and insulating layers, each typically being between 1-30 angstroms thick, using physical vapor deposition (PVD) methods. Each layer must be precisely measured and controlled. Magnesium oxide (MgO) film is the core of the magnetic tunnel junction (MTJ), a critical layer that forms the barrier between the free layer and reference layer. It needs to be deposited at 0.1 angstrom precision to repeatedly achieve low area resistance (RA typical range from 5-10Ωµm2) and tunnel magnetoresistance (TMR >150%) characteristics. TMR is a critical parameter that dictates device performance, yield and endurance. Missing atoms can significantly affect TMR (Figure 1), which explains why metrology is so critical in MRAM manufacturing.

Figure 1. Variability of a few atoms in the critical MgO layer impacts performance.

While PCRAM and ReRAM layers are not as thin as MRAM, the materials are highly susceptible to impurities and degradation upon exposure to atmosphere. As with MRAM, this calls for an integrated PVD process system capable of depositing and measuring multiple materials under vacuum to prevent particles and impurities from contaminating the device.

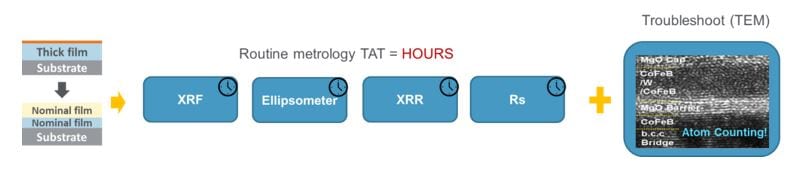

In fabricating these next-generation memories, variability control is critical to achieving repeatable performance for volume manufacturing and commercialization. To achieve <0.3V variability within the wafer threshold voltage (Vt) spread, critical layers in the PCRAM stack must be controlled to within ±5 angstroms of the target thickness, which in turn requires metrology capable of sub-angstrom precision. Traditional characterization approaches for such film stacks rely on a host of standalone metrology techniques and transmission electron microscopy (TEM) that are separated from the process tools, resulting in potential for film degradation.

Figure 2. Traditional metrology approaches have a longer turnaround time and are limited in measuring individual layer thicknesses in a stack.

Most thin films change properties when exposed to atmosphere, so traditional atmospheric metrology relies on thicker blanket films for chamber monitoring, which is not always representative of the material properties of ultra-thin films. Such an approach consumes more deposition material and tool time for chamber qualification.

Although TEM can resolve individual thin layers, as can be seen in Figure 2, the definition of what constitutes an “edge” and precise determination of the layer thickness becomes a problem when the layers are no more than a couple of atoms thick. This situation requires a metrology system that inherently considers the statistical nature of the process. Additionally, longer time to results (hours to days), imprecisely measuring buried film properties and the inability to monitor a full stack on patterned wafers are driving the need for new metrology techniques.

Integrated platforms that operate under vacuum across multiple process steps are needed to minimize queue time effects, avoid film degradation and interface issues. Additionally, they open the door for close loop control of each layer in the stack, thus reducing variability.

For new memories to reach high-volume manufacturing, the industry must enable new process control solutions. Those systems should measure pristine, as-deposited thin films, have a small footprint, and operate quickly and non-invasively.

Tags: metrology, Process Control, MRAM, PCRAM, ReRAM, merging memories

Niranjan Khasgiwale

Vice President, Imaging and Process Control Group

Niranjan Khasgiwale is a vice president in the Imaging and Process Control group at Applied Materials, responsible for real-time measurement and control solutions. He has more than 20 years of marketing experience in the semiconductor equipment industry. Niranjan holds a master’s degree and Ph.D. in materials science from Dartmouth College and Lehigh University respectively, and a B.Tech in metallurgy from the Indian Institute of Technology.

Adding Sustainability to the Definition of Fab Performance

To enable a more sustainable semiconductor industry, new fabs must be designed to maximize output while reducing energy consumption and emissions. In this blog post, I examine Applied Materials’ efforts to drive fab sustainability through the process equipment we develop for chipmakers. It all starts with an evolution in the mindset of how these systems are designed.

Innovations in eBeam Metrology Enable a New Playbook for Patterning Control

The patterning challenges of today’s most advanced logic and memory chips can be solved with a new playbook that takes the industry from optical target-based approximation to actual, on-device measurements; limited statistical sampling to massive, across-wafer sampling; and single-layer patterning control to integrative multi-layer control. Applied’s new PROVision® 3E system is designed to enable this new playbook.

Breakthrough in Metrology Needed for Patterning Advanced Logic and Memory Chips

As the semiconductor industry increasingly moves from simple 2D chip designs to complex 3D designs based on multipatterning and EUV, patterning control has reached an inflection point. The optical overlay tools and techniques the semiconductor industry traditionally used to reduce errors are simply not precise enough for today’s leading-edge logic and memory chips.