Products & Technologies

Products & Technologies

Services

Resources

Posted

March 11, 2019

Stay updated on our content.

Creating Higher-Performance, Lower-Power Transistors with Selective Removal Technologies

by Matt Cogorno, Toshihiko Miyashita

Mar 11, 2019

Remember when we could charge our mobile phones on a Sunday and not even think about it again until the next weekend? There was a time when battery life wasn’t even in the top ten concerns when purchasing a mobile phone. Today however, smartphones are constantly being used for computing, gaming, video streaming and other power-hungry applications, so battery life matters more than ever.

Classic Moore’s Law scaling used to provide simultaneous improvements in chip “PPAC”—power, performance and area/cost—but that is no longer the case as 2D scaling has reached physical limits. Moving forward, PPAC improvements will be achieved through a combination of approaches including new ways to shrink transistors. It’s no longer sufficient to simply make transistors smaller; we also need to improve power-efficiency to deliver maximum performance in a small form factor.

One way to improve battery life in mobile devices is to make sure transistors are really off when they should be. Ideally, when a transistor is in the “off” state, there shouldn’t be any current flowing through the transistor fin channel and gate. In the real world however, there is always a small amount of current that leaks through the channel, junctions and gate dielectric (called Ioff). So manufacturers constantly work to keep those leaks to a minimum.

Traditionally Ioff has been reduced through increased control on the gate. A great example of this is the innovation of the FinFET. In this scheme, the entire transistor is stretched in the vertical direction so that the channel is raised out of the substrate and the gate wraps around the three sides of the fin. The gate’s larger contact area in a certain 2D footprint allows better control of leakage current.

Most of the drive current in the silicon fin of the FinFET flows close to the surface of the material rather than the middle of the fin, and the total current is almost proportional to fin perimeter (effective channel width). That means as we narrow the fins and fin pitch and/or reduce the number of fins per transistor to include more transistors per wafer, we need to also make them taller to compensate (Figure 1); however, there are significant engineering challenges to thinning, shaping and increasing the height of the fin.

Figure 1. Evolution of the fin profile from 22nn to 10nm shows higher and narrower profiles are required for higher drive current and better electrostatics [1-3]. Schematic shows the fin profile and key physical parameters.

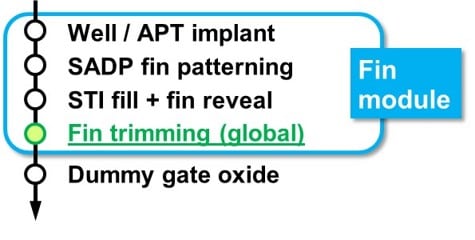

One key scaling factor is narrowing the space or pitch between fins to reduce the overall device footprint. It is very challenging to pattern narrow fins with narrow pitch, so the industry standard approach is to pattern the fins to a manageable width and pitch, and then trim them afterwards. This is traditionally achieved by oxidizing the top few surface nanometers of the fin, then using a wet chemistry to remove the thin oxide layer in a single step. This "global fin trim” approach etches all fins at the same rate for maximum controllability, but also creates serious challenges for advanced devices.

Figure 2. Process flow for global fin trimming after fin reveal.

The first issue with global fin trim involves the mechanical strength of the fins after trimming. In the flow shown in Figure 2, there are many thermal processes after fin trim, creating stresses that affect the inner and outer fins differently. This can cause the fins to fan out like peacock feathers, and that distortion creates differences in fin channel stress and therefore channel mobility.

The second challenge occurs because global fin trimming trims the channel and the source and drain (S/D) regions at the same time. If the S/D are narrowed, the access resistance will go up and negate any benefit of the fin trim in the first place.

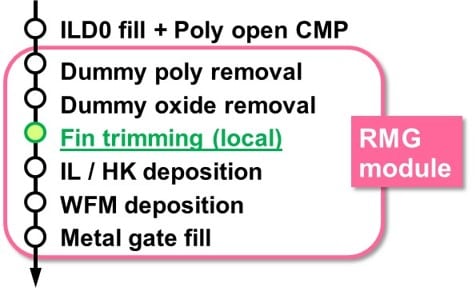

Resolving these issues requires an innovative way to trim only the channel region while leaving the S/D areas untouched. In a paper we presented at the recent IEDM conference[4], we showed the capability of using a selective etch technology to trim silicon fins after dummy gate removal.

In this "local silicon fin trim” scheme, shown in Figure 3, the untrimmed fins retain the maximum mechanical strength during the steps between fin formation and metal gate. As a result, they are less susceptible to deformation during subsequent steps. An added benefit of this new process is that the S/D are not exposed, so the trimming is limited to the channel. This gives us the ability to create the exact profile that we need: narrow channel, wide source and drain, with minimal fin deformation.

Figure 3. Process flow for local fin trimming after dummy gate removal preserves mechanical strength of the fin for subsequent process steps.

The key to unlocking this performance boost is the ability to controllably etch only two nanometers of silicon using the Producer® Selectra™ Etch system. This is the equivalent of removing a single atomic layer of silicon from the surface of the wafer. To make things even more challenging, we need to have extreme selectivity to oxide and nitride to prevent damage to spacer or other materials (low k films). In our recent paper we demonstrated the feasibility of this scheme with precise etch control and even improved line edge roughness of the silicon fin (LER 2.1nm pre, 1.8nm post). These physical results were validated to achieve a ~10 percent improvement in Ion at a fixed Ioff (or a ~50 percent Ioff reduction at a fixed Ion) compared to the control device (no local fin trimming).

This result is a great example of Applied’s “New Playbook” for semiconductor design and manufacturing using new materials-based approaches to enable PPAC improvements for advanced devices.

[1] C. Auth et al., “A 22nm high performance and low-power CMOS technology featuring fully-depleted Tri-Gate transistors, self-aligned contacts and high density MIM capacitors,” 2012 Symp. VLSI Tech. Dig., pp. 131-132

[2] S. Natarajan et al., “A 14nm logic technology featuring 2nd-generation FinFET transistors, air-gapped interconnects, self-aligned double patterning and a 0.0588um2 SRAM cell size,” 2014 IEDM Tech. Dig., pp. 71-73

[3] C. Auth et al., “A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects,” 2017 IEDM Tech. Dig., pp. 673-676

[4] T. Miyashita et al., “Selective fin trimming after dummy gate removal as the local fin width scaling approach for N5 and beyond,” 2018 IEDM Tech. Dig., pp. 827-830

Tags: FinFET, transistors, Moore’s Law, etch, selective removal

Matt Cogorno

Director of Global Product Management

Matt Cogorno is director of global product management at Applied Materials. He holds B.S. degrees in physics and applied mathematics from the University of Oregon.

Toshihiko Miyashita

Senior Member of Technical Staff

Toshihiko Miyashita is a senior member of technical staff in the Advanced Product Technology Development group at Applied Materials. He is an expert on front end of line integration and device development. He holds more than 10 U.S. patents and has authored or co-authored over 60 peer-reviewed journal and conference papers.

Adding Sustainability to the Definition of Fab Performance

To enable a more sustainable semiconductor industry, new fabs must be designed to maximize output while reducing energy consumption and emissions. In this blog post, I examine Applied Materials’ efforts to drive fab sustainability through the process equipment we develop for chipmakers. It all starts with an evolution in the mindset of how these systems are designed.

Innovations in eBeam Metrology Enable a New Playbook for Patterning Control

The patterning challenges of today’s most advanced logic and memory chips can be solved with a new playbook that takes the industry from optical target-based approximation to actual, on-device measurements; limited statistical sampling to massive, across-wafer sampling; and single-layer patterning control to integrative multi-layer control. Applied’s new PROVision® 3E system is designed to enable this new playbook.

Breakthrough in Metrology Needed for Patterning Advanced Logic and Memory Chips

As the semiconductor industry increasingly moves from simple 2D chip designs to complex 3D designs based on multipatterning and EUV, patterning control has reached an inflection point. The optical overlay tools and techniques the semiconductor industry traditionally used to reduce errors are simply not precise enough for today’s leading-edge logic and memory chips.