Endura® Volta® Selective W CVD

텅스텐(W)은 낮은 저항과 벌크 충진 특성으로 인해 반도체 전체 공정 중 중간공정(MOL) 전극에서 갭 충진 재료로 널리 사용되었습니다. MOL 전극은 트랜지스터 와 금속배선(interconnect)을 잇는 중요한 전기적 연결을 형성합니다. 따라서 전반적인 소자 성능을 위해 저항성이 낮은 전극 형성이 필수적입니다.

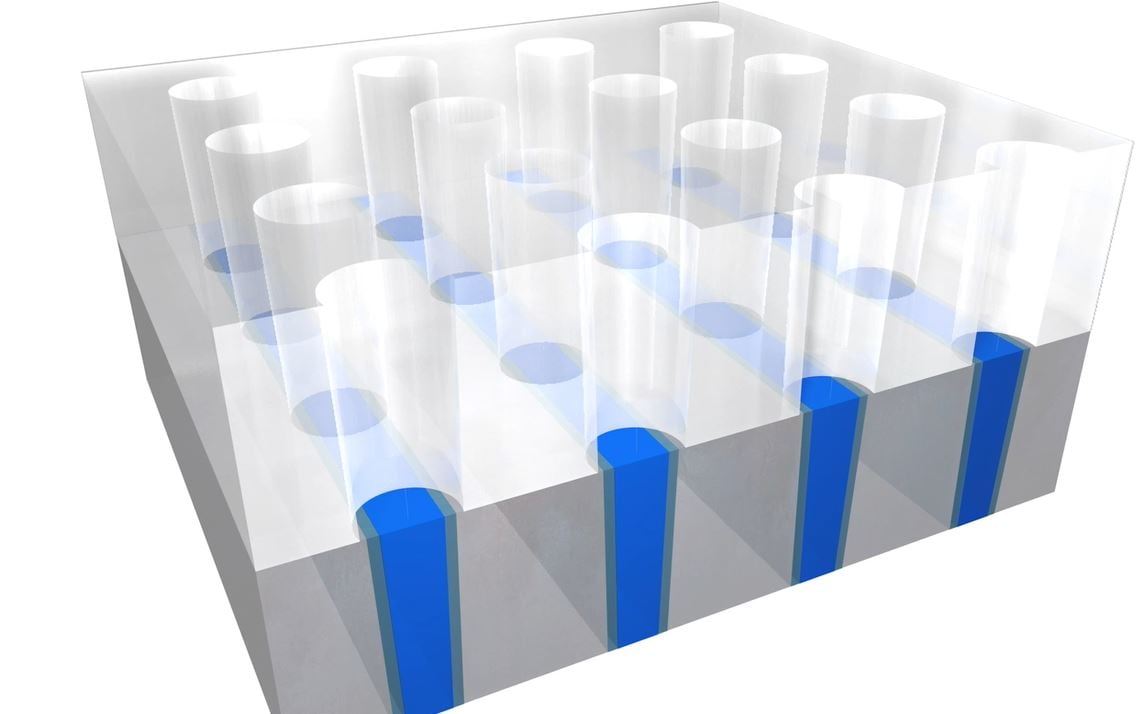

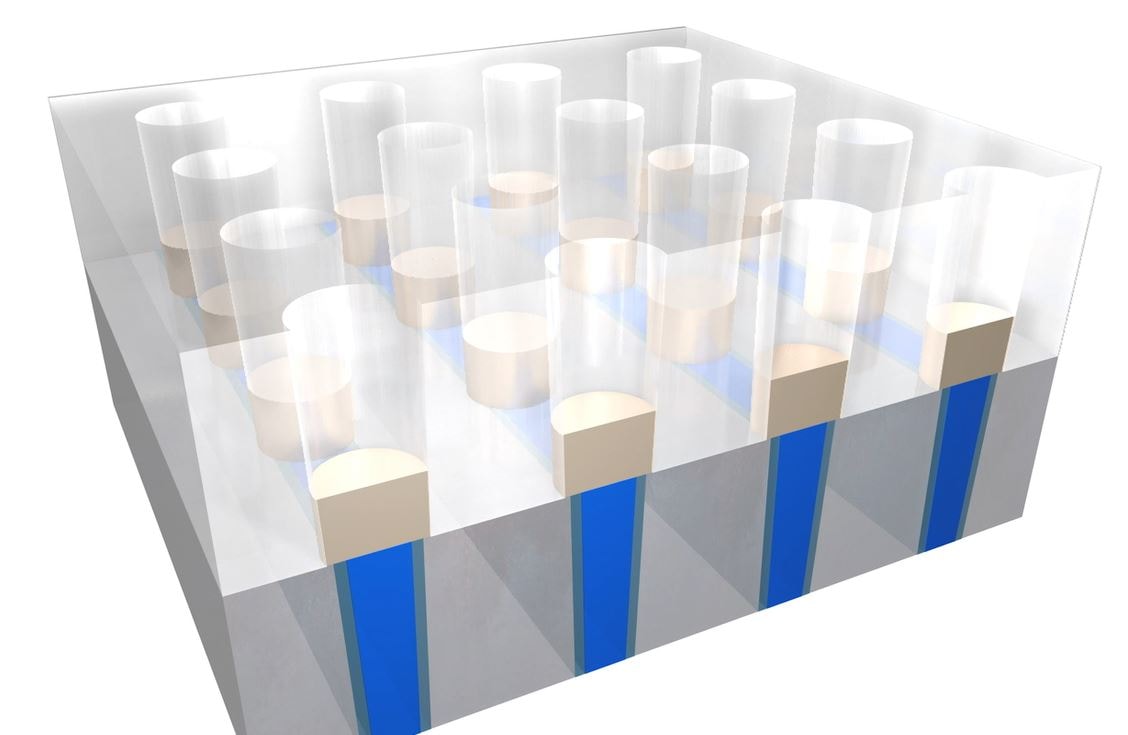

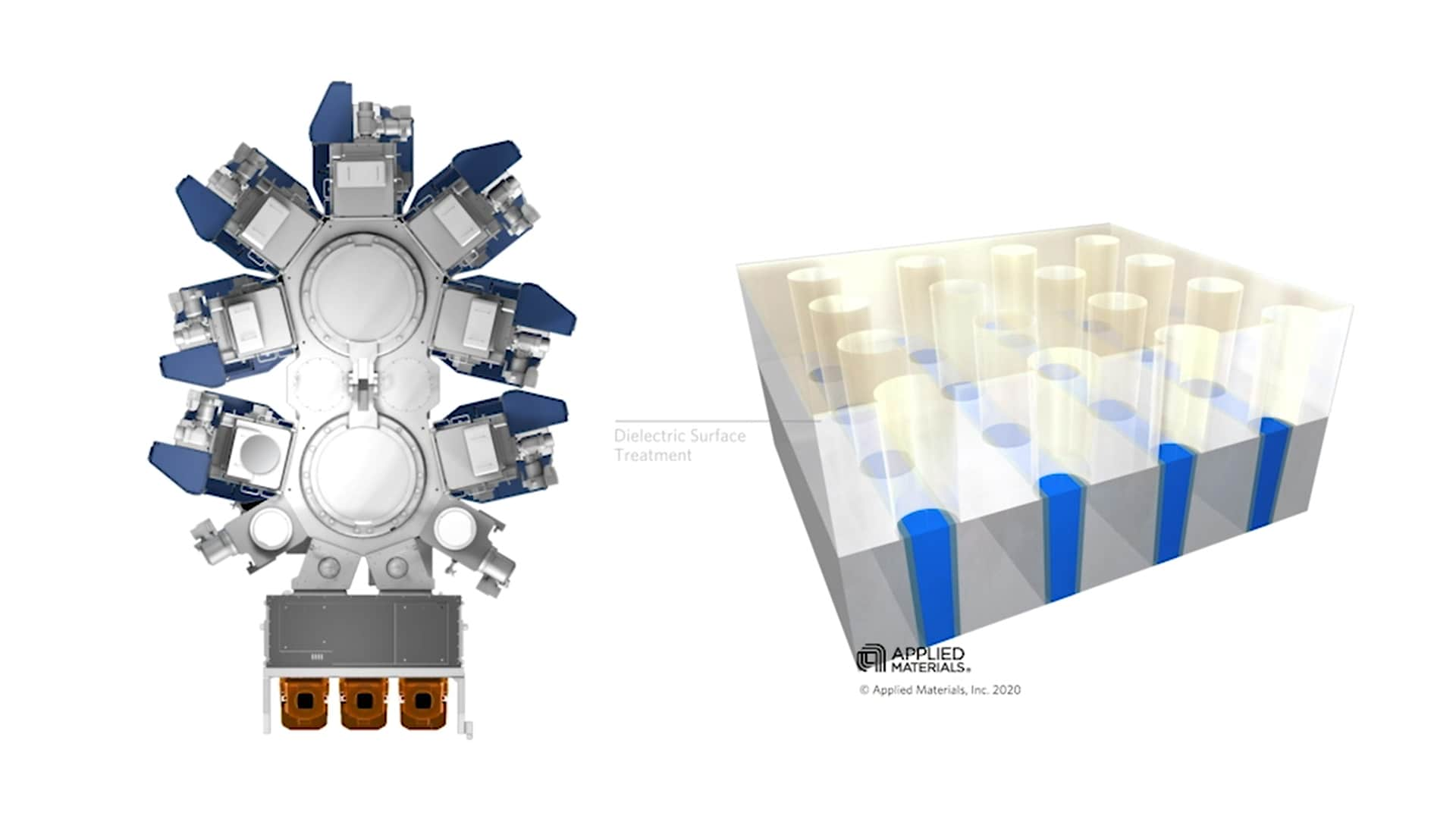

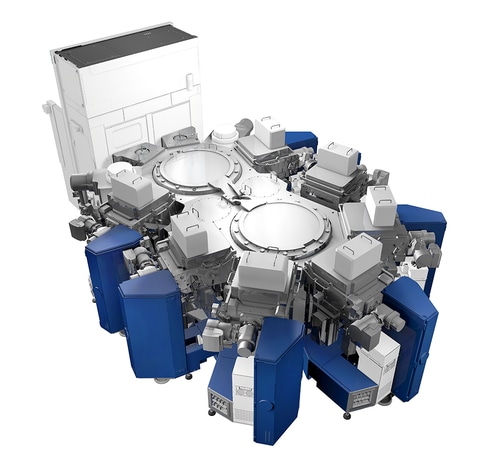

Applied Endura Volta Selective W CVD 시스템은 2D 미세화 혁신을 통해 이러한 부작용을 완화하는 통합 소재 솔루션(IMS™)을 제공합니다. 이 시스템은 표면 처리 챔버와 선택적 텅스텐 증착 챔버를 결합합니다. 선택적 증착은 증착 챔버의 고유한 공정 성능과, 밑에서 위로, 그리고 금속 위에 금속을 증착하기 위해 특수 화학 물질을 사용하여 전극의 하부 금속 및 유전체를 준비시키는 다양한 표면 처리에 의해 구현됩니다. 선택적 공정은 라이너/배리어 층과 핵 생성층을 모두 제거하여 소자 성능의 병목 현상을 완화하고 공극과 이음매(접합선) 없는 갭필을 구현합니다.

Applied Endura Volta Selective W CVD 시스템은 2D 미세화 혁신을 통해 이러한 역효과를 제거하는 통합 재료 솔루션을 제공합니다. 이 시스템은 표면 처리 챔버와 선택적 텅스텐 증착 챔버를 결합합니다. 선택적 증착은 특수 화학 물질을 사용하여 기본 금속과 컨택 유전체를 준비함으로써 상향식 금속 대 금속 증착을 가능케 하는 증착 챔버와 다양한 표면 처리의 고유한 공정 기능에 의해 구현됩니다. 선택적 공정은 라이너/베리어 층과 핵 생성층을 모두 제거하여 소자 성능의 병목 현상을 완화하고 공극과 빈틈이 없는 갭 충진을 구현합니다.

모든 공정 단계가 매우 깨끗하고 연속적인 고진공 환경에서 이루어지므로 통합 재료 솔루션은 오염되지 않은 경계와 결함이 없는 컨택 충진을 보장합니다. 전도성 금속의 체적이 최대화됨에 따라 컨택 저항성이 기존 라이너/베리어 층 컨택 제조와 비교하여 크게 향상되었습니다. 이러한 낮은 저항은 높은 소자 밀도를 촉진하고 2D 미세화를 확장합니다.

기존 컨택 갭 충진에서는 전도성 금속의 체적이

라이너/베리어 층 및 핵 생성층에 의해 제한됩니다.

선택적 텅스텐은 컨택의 전체 체적을

전도성 금속에 사용할 수 있도록 해줍니다.

선택적 증착을 위한 IMS는 특수 표면 전처리와 고유한 텅스텐 증착 공정을 포함합니다.

고유한 텅스텐 증착 공정과 결합합니다.

Endura® Volta® Selective W CVD