半導体

市場と変化

ソリューションとソフトウェア

AI時代を可能にする

IoT、ビッグデータ、AIの急速な普及に伴い、チップの消費電力、性能、面積あたりコスト、そして市場投入までの期間(PPACt™)の迅速かつ大幅な改善が求められています。この課題が、業界における新しい取り組み「New Playbook」を推し進める原動力となっています。これらの要件を満たすため、全ての産業が関わる新しい形でのコラボレーションが始まっています。私たちは、シリアルイノベーションではなく、パラレルイノベーションを選択し、マテリアルからシステムまで(Materials to Systems™)とシステムからマテリアルまで(Systems to Materials™)に至るエコシステムを通して広範な協業を促進し、AI時代に対応する改良したチップの提供を加速していきます。

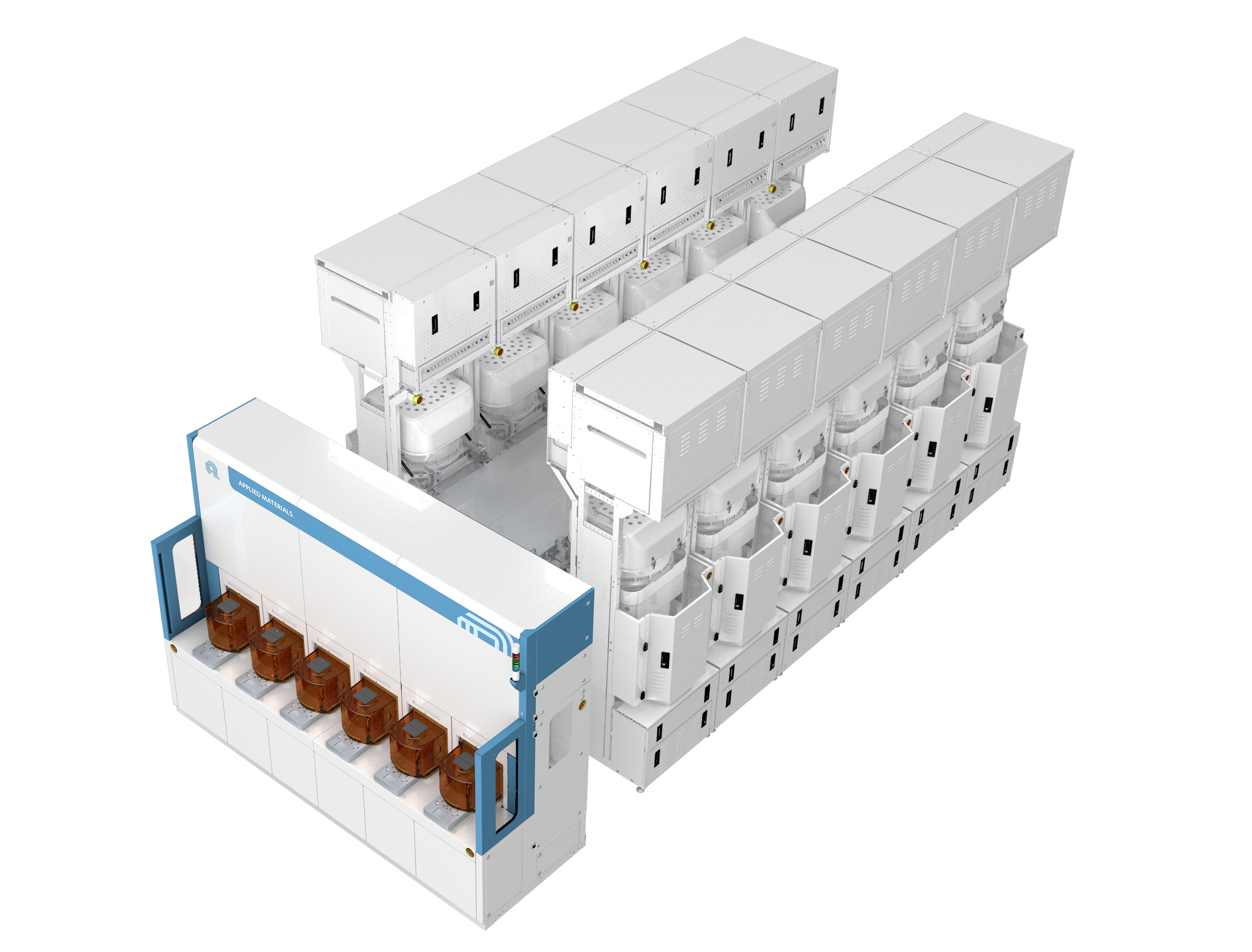

PPACtイノベーション

アプライド マテリアルズは、お客さまとパートナー企業に向けて、PPACtの改善を目指す「New Playbook」を促進しています。私たちは、最も広範で包括的な製品ラインアップを揃え、PPACtにおけるイノベーションを提供します。このラインアップにより、マテリアルとデバイスの新しい形での創出と成膜、成型と除去、加工、解析、および接続する技術をもたらします。 私たちは、1つの傘の下に幅広いプロセス技術と計測の技術を有し、半導体とパッケージングの研究開発施設を備えた唯一無二の企業です。当社のインテグレーテッド マテリアル ソリューション®テクノロジーは、マテリアルの成膜、除去、加工、および解析を協調最適化することにより、最先端ノードの高性能かつ低消費電力なチップの製造に向けた新しいマテリアルの創出と新しい構造を提供します。

ネットゼロ加速化

アプライド マテリアルズは、装置を設計するにあたって耐久性、アップグレード性、新たなアプリケーションへの転用性を重視するとともに、パーツの不具合や性能が基準以下に劣化した場合に修理が容易に行えるよう工夫しています。 新たに製造されるパーツはどれも修理性を考慮して設計されているほか、修理とや再生にあたっては可能な限りリファビッシュパーツを利用し、サステナビリティとコスト効率を高めています。 業界のリーダーという特異の立場には従業員、お客さま、社会に対する大きな責任が伴うということを認識しています。だからこそ、アプライド マテリアルズは製造装置を根本からグリーン化し、ネットゼロイニシアチブを推進しているのです。

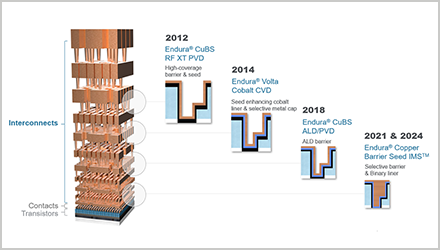

Advancing Chip Performance with 30 Years of Wiring Leadership

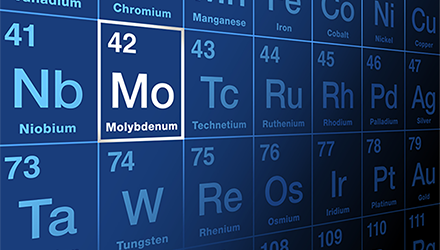

Co-optimized Process and Metrology Accelerates Molybdenum Contact Development

Applied Materials Hosts Lively Debate on AI Energy Efficiency