半導体

市場と変化

ソリューションとソフトウェア

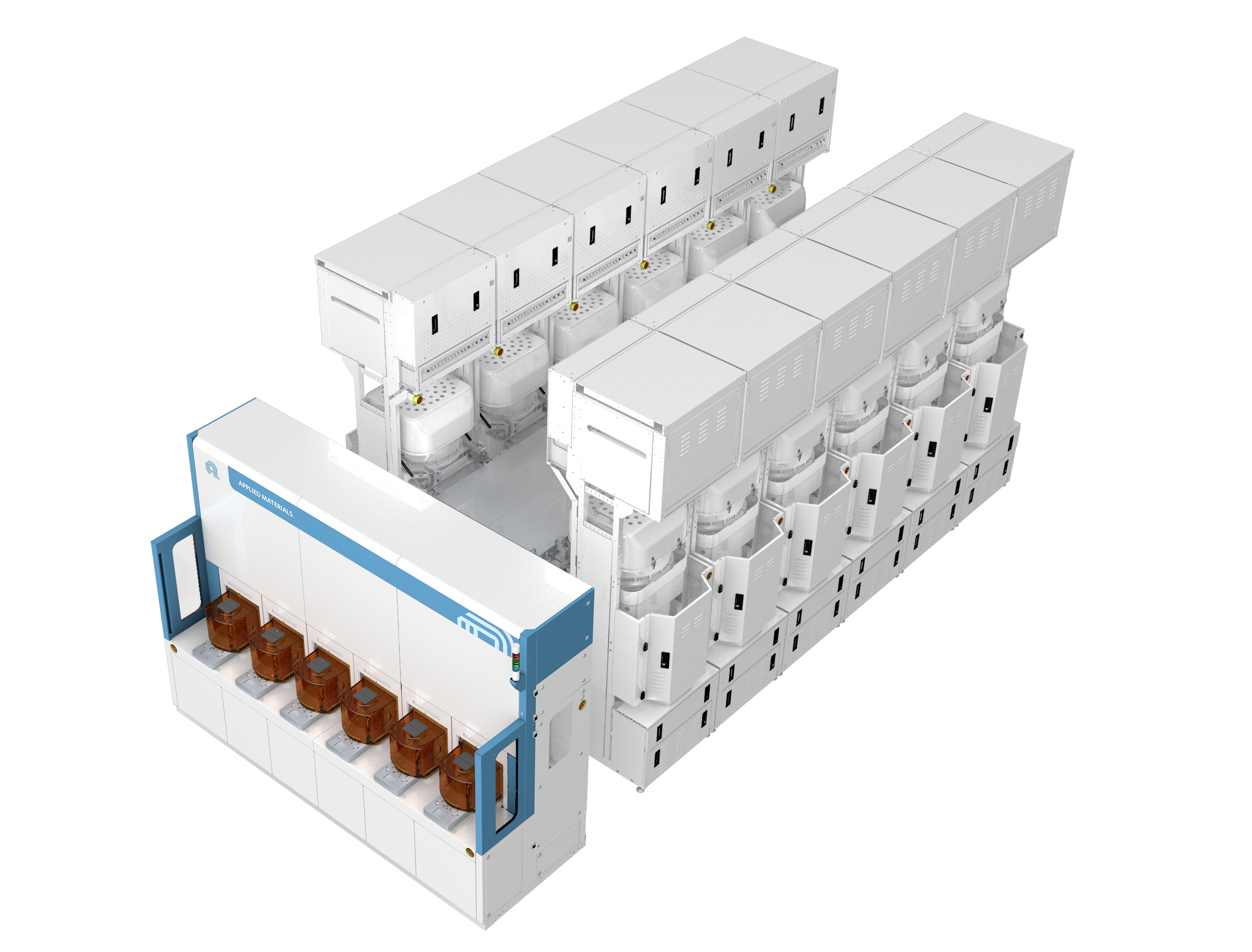

半導体チップ製造用システムの設計・製造

AI時代を可能にする

AI 時代では、チップの電力効率とパフォーマンスの急速かつ劇的な改善が求められます。この挑戦は、新しい方法で革新とコラボレーションを実現し、新技術の商業化を加速するというアプライド マテリアルズのビジョンの原動力です。エコシステム全体で連携を強化することで、AI 時代に向けた改良されたチップの提供が可能になります。

技術の転換点に向けたイノベーション

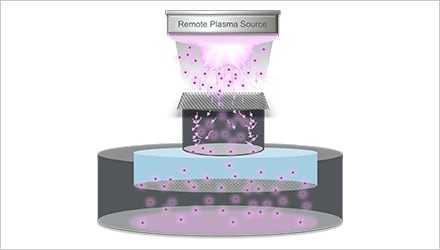

当社は、幅広い機能とテクノロジーのポートフォリオを結び付けることで、差別化されたソリューションを成長させてきました。当社の幅広く連携した製品ポートフォリオは、新しい方法で材料やデバイスを生成、成膜、形成、除去、改質、解析、接続します。当社のIntegrated Material Solution® 技術は、一連のプロセス テクノロジーと計測機能を 1 つの傘の下に統合し、マテリアルの成膜、除去、改質、解析を協調最適化して、最先端ノードの高性能、低消費電力チップ向けの新しい材料を生み出し、新しい構造を設計します。

持続可能性の加速

当社のシステムは、長期間の使用が可能で、アップグレードや新しいアプリケーションへの再利用をサポートするように設計されています。新しく製造されたすべてのシステムコンポーネントと部品は、修理性を高めるように設計されており、可能な限り再生部品を使用することで、持続可能性とコスト効率の向上に貢献しています。当社は、お客様の事業運営の持続可能性を向上させるファブおよびサブファブの技術とサービスを継続的に開発しています。当社は、独自のリーダーシップの立場には、従業員、顧客、そして社会に対する大きな責任が伴うことを認識しています。

Unlocking Next-Gen AI Chips Through Advanced Materials Modification

The Angstrom Era Explained: New Master Class Series Kicks Off April 8

Applied Materials Convenes Industry Leaders on Advanced Patterning for the AI Era