Products & Technologies

Products & Technologies

Services

Resources

Posted

April 16, 2020

Stay updated on our content.

The Future of Logic Depends on Heterogeneous Design and Integration

Apr 16, 2020

The Internet of Things (IoT), Big Data and AI are exerting new demands on performance, power, area-cost and time-to-market (PPACt) that exceed the bounds of classic Moore’s Law scaling. This is spurring a combination of approaches that Applied calls the “New Playbook.” A key pillar of the playbook is advanced packaging, which is shorthand for heterogenous design and integration of what can be a wide array of similar or dissimilar chips. Designers can now integrate CMOS chips of various nodes and wafer sizes with other functions including power, RF and photonics. They can combine silicon sourced from different IDMs and foundries to create heterogeneous chips, subsystems or highly integrated systems. In short, it’s about enabling new levels of design and manufacturing flexibility to address chip PPACt.

Recently, several of my colleagues posted blogs about an outstanding panel discussion held at the most recent IEEE International Electron Device Meeting (IEDM) in San Francisco. Titled, “The Future of Logic: EUV is Here, Now What?,” the panel was hosted by my colleague Regina Freed and featured experts from Facebook, IBM Research, Intel, Stanford University and TSMC. I’ll highlight the panelists’ perspectives on heterogeneous design and advanced packaging and share some of the innovative work Applied is doing in this area to help enable the next decade of progress in logic.

The panelists discussed two megatrends that can benefit from advanced packaging: cloud computing and 5G. Hyperscale computing architects are looking for new ways to enable higher performance at constant or lower power. 5G infrastructure and device designers also prioritize signal integrity, form factor, thermal dissipation and cost.

Heterogeneous design and advanced packaging offer new ways beyond 2D scaling to achieve the optimizations engineers are looking to achieve. Functional system blocks that don’t demand leading-edge nodes can be fabricated on trailing-node geometries, potentially re-using existing logic designs. This can reduce silicon cost, shorten design time and accelerate time to yield and market, which are key benefits to establishing leadership in promising new markets. Additionally, advanced packaging can be used to shorten chip interconnects and reduce parasitics to significantly improve data rates and overall performance.

“I am a big believer in advanced packaging as an enabler of Moore's Law moving forward,” said Ramune Nagisetty, Senior Principal Engineer and Director of Process and Product Integration Technology Development Group at Intel, during the panel. “The future is about specialization at scale with advanced packaging and interoperable chiplets. I foresee that an industry scale ecosystem will evolve around the concept of a chiplet library where you can swap out an older technology node for a new technology node, for example, in high-speed cores. And then you can mix in specialized nodes for specific functionality like power delivery, or memory, or specific types of accelerators like GPUs. This is basically bringing high-resolution fab technology into the advanced packaging arena.”

To that end, Applied Materials is enabling the industry to develop breakthroughs in heterogenous integration at our Advanced Packaging Development Center in Singapore. This facility is among the most advanced wafer-level packaging labs in the world. It’s where we are joined by industry partners to research and develop advanced packaging equipment, processes and device structures, in a 17,300 square foot Class 10 cleanroom with full lines of wafer-level packaging equipment. Candidate packages are designed, modeled, simulated, fabricated and fully tested to develop the enabling process technologies that meet emerging industry needs.

Applied Materials’ Advanced Packaging Development Center in Singapore is one of the most advanced wafer-level packaging labs in the world.

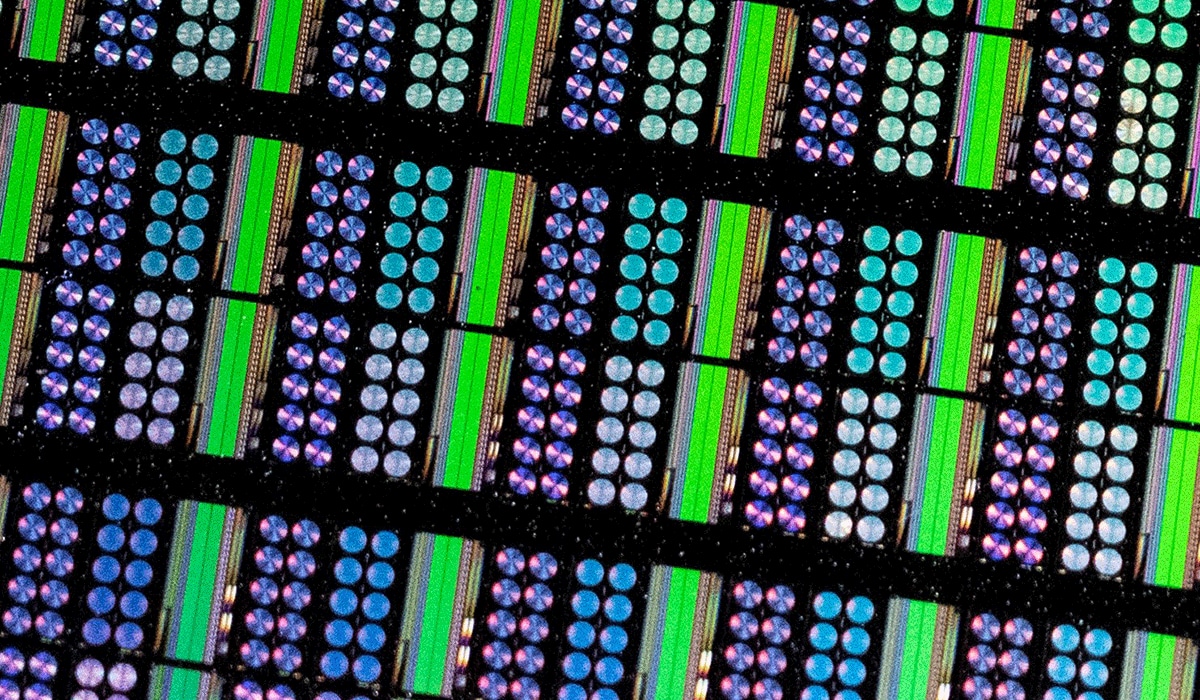

Working with our partners, we are focused on developing wafer-level systems and process technology solutions to enable the future roadmap of heterogenous packaging integration. We achieve this by enabling the foundational “building blocks” of heterogenous integration, namely advanced bump and microbump (1D), fine-line redistribution layer (RDL-2D), through-silicon via (TSV-3D) and hybrid bonding interconnect (HBI-3D). In addition to unit-level processes, we are developing full-flow solutions for these building blocks and validating them through our internally designed test vehicles. We are also working with customers to develop customized packaging solutions, tailoring and prototyping these building blocks at our Advanced Packaging Development Center before transferring the comprehensive solution over to our customers’ high-volume manufacturing facilities.

Our Advanced Packaging Development Center is a great example of how we are aligning our research and development to accelerate the “New Playbook.” Finding new ways to mix, match and integrate silicon will enable better PPACt for our customers and the AI Era of computing.

Tags: IEDM, PPACt, Advanced Packaging, logic, heterogeneous integration, Heterogeneous Design, iot, Big Data, Moore's Law, AI, New Playbook

Nirmalya Maity, Ph.D.

Corporate Vice President - Advanced Packaging

Nirmalya Maity is corporate vice president of Advanced Packaging at Applied Materials. Previously, he was at Cabot Corporation where he held several key leadership positions including Chief Technology Officer and vice president of Corporate Strategy & Development. Prior to Cabot, Nirmalya worked for Applied Materials in various technology and product management leadership roles. He received his Ph.D. in chemical engineering from Cornell University and bachelor of science in chemical engineering from the Indian Institute of Technology, Roorkee.

Now is the Time for Flat Optics

For many centuries, optical technologies have utilized the same principles and components to bend and manipulate light. Now, another strategy to control light—metasurface optics or flat optics—is moving out of academic labs and heading toward commercial viability.

Seeing a Bright Future for Flat Optics

We are at the beginning of a new technological era for the field of optics. To accelerate the commercialization of Flat Optics, a larger collaborative effort is needed to scale the technology and deliver its full benefits to a wide range of applications.

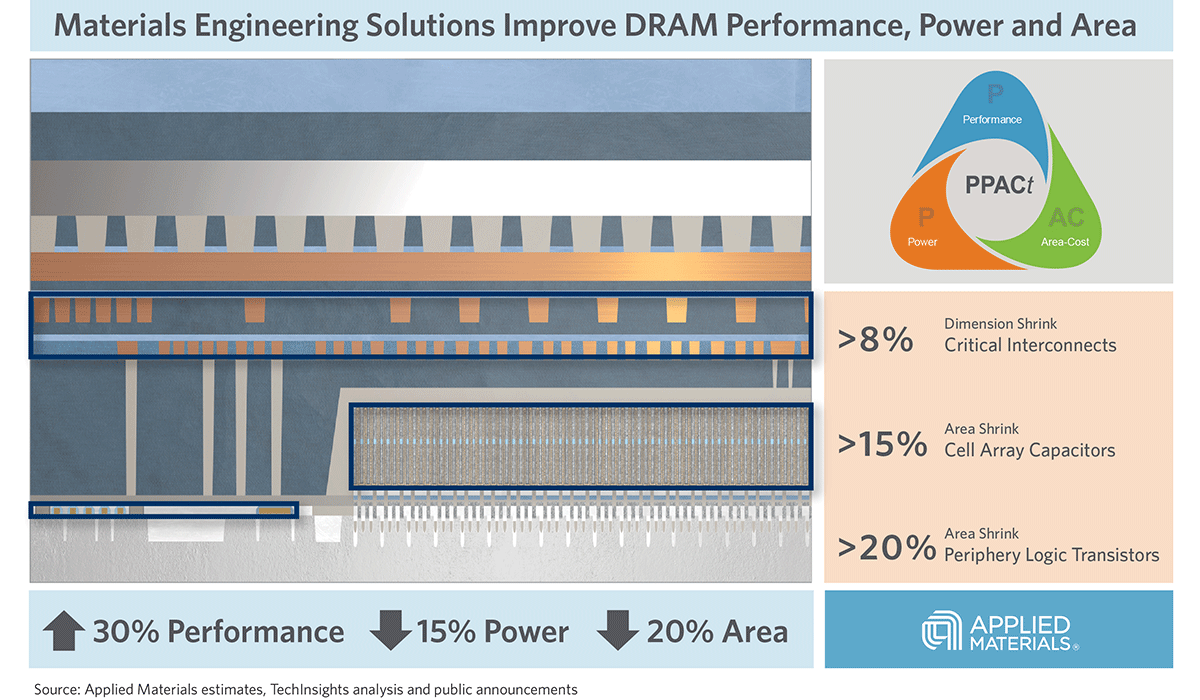

Introducing Breakthroughs in Materials Engineering for DRAM Scaling

To help the industry meet global demand for more affordable, high-performance memory, Applied Materials today introduced solutions that support three levers of DRAM scaling.