應用材料公司推出 DRAM 微縮的材料工程解決方案

| 新聞聯絡人: | 台灣應用材料 譚鳳珠 |

| 聯絡電話: | 03-579-3958 |

| email: | pearl_tan@amat.com |

| 發稿日期: | 民國 110年5月11日 |

| 本新聞稿譯自總公司發佈的新聞稿 | |

- 全新 Draco™ 硬質光罩材料與 Sym3® Y 蝕刻系統共同最佳化,可加快 DRAM 電容器微縮進程

- DRAM 製造商採用應材率先推出的 Black Diamond® 低 k 值介電材料技術,克服邏輯電路中的導線互連微縮挑戰

- 高 k 值金屬閘極電晶體現已導入先進 DRAM 設計之中,藉此提高效能並降低功耗,同時縮小周邊邏輯電路以改善面積和成本效益

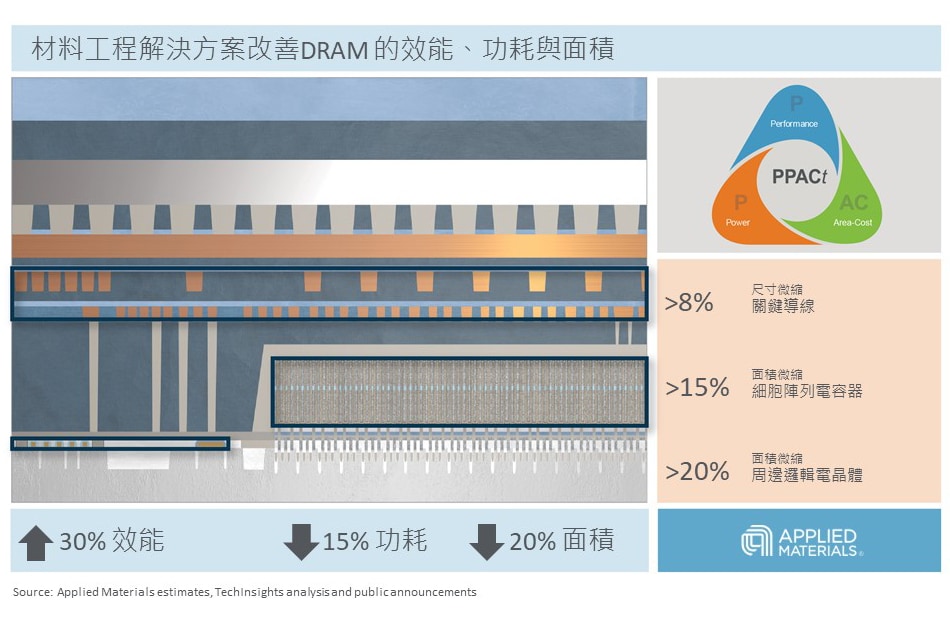

應用材料公司發布一款材料工程解決方案,為記憶體客戶提供三種新方法,進一步微縮 DRAM 並加速改善晶片效能、功耗和單位面積成本和上市時間 (PPACt)。

在全球經濟數位轉型的帶動下,DRAM 的市場需求不斷創造新高。物聯網在終端建立數千億個新型運算裝置,促使傳輸到雲端處理的資料激增。業界迫切需要突破,以利實現 DRAM 微縮,進而減少面積和成本,同時以更高的速度和更低的功耗運作。

應用材料公司正與 DRAM 客戶合作,將三種材料工程解決方案商業化,進而推出新方法來進行微縮、改善效能和功耗。這款解決方案適用於 DRAM 晶片的三項領域:儲存電容器,金屬導線互連佈線和邏輯電晶體。這些裝置正逐漸投入大量生產,並有望在未來數年內顯著增加應材 DRAM業務的營收。

電容器微縮專用的 Draco™ 硬質光罩

由於記憶體陣列佔 DRAM 晶粒面積超過 55%,因此提高這些記憶單元的密度是降低每位元成本的最佳方法。資料是以電荷形式儲存在垂直排列的圓柱形電容器中,而這些電容器需要盡量擴大表面積,以容納足夠數量的電子。DRAM 製造商將電容器窄化的同時,也將其拉長以形成最大的表面積。在 DRAM 微縮方面,新的技術挑戰已經出現:電容深孔的蝕刻可能超過「硬質光罩」材料的極限,這些硬質光罩提供印刷模板的作用,可據以決定各條圓柱放置何處。如果硬質光罩被蝕穿,圖形就會遭到破壞。增加硬質光罩高度是不可行的做法,因為硬質光罩和電容孔洞的總深度若超過特定限制,則會殘留蝕刻副產物,並導致電容孔洞彎曲、扭曲和不均勻的深度。

解決方案就是 Draco™ 新推出的硬質光罩材料,其已與應材的 Sym3® Y 蝕刻系統共同進行最佳化,而此流程則是採用應材 PROVision® eBeam 測量和檢驗系統,以每小時將近 50 萬次的測量加以監控。Draco 硬質光罩將蝕刻選擇比提高超過 30%,因此可以降低硬質光罩的高度。Draco 硬質光罩和 Sym3 Y 共同最佳化的功能包括先進 RF 脈衝技術,可與蝕刻工序同步移除副產物,進而使曝光孔呈現完全筆直且均勻的圓柱形。PROVision eBeam 系統可為客戶提供大量、即時且可行的硬質光罩臨界尺寸均勻度資料,而這項參數是決定電容器均勻度的關鍵所在。使用應材的解決方案,客戶可將局部臨界尺寸均勻性提高 50%,並將橋接缺陷減少 100 倍,進而改善良率。

應用材料公司半導體產品事業群集團副總裁拉曼.阿丘塔拉曼 (Raman Achutharaman) 表示:「為了協助客戶迅速解決材料工程方面的挑戰,最有效的方法是將相鄰步驟共同最佳化,並使用大量測量和 AI 技術來優化製程變數。」

將 Black Diamond® 低 k 值介電材料技術引進 DRAM 市場

在 DRAM 微縮方面,第二項關鍵方法是縮減金屬導線互連佈線所需面積來降低晶粒的面積,而此佈線的作用是對訊號進出記憶體陣列進行聯通。每條金屬線皆由絕緣介電材料包覆,以防止資料訊號彼此干擾。在過去 25 年中,DRAM 製造商採用兩種氧化矽 - 矽烷(Silane)和四乙氧基矽烷 (TEOS) - 的其中之一作為介電材料。隨著介電層不斷變薄,DRAM 晶粒尺寸也逐漸縮小,從而帶來了新的技術挑戰:目前的電介質太薄,無法防止金屬線路內部電容耦合,導致訊號彼此干擾,進而提高功耗、降低效能,增加溫度並減損可靠性。

解決方案就是 Black Diamond®,一種率先用於先進邏輯晶片的低 k 值介電材料技術。隨著 DRAM 設計面臨類似的微縮挑戰,應材採用 Black Diamond 因應 DRAM 市場需求,並透過高生產力的 Producer® GT 平台供應。DRAM 專用的 Black Diamond 可實現更小、緊密的金屬導線互連佈線,能以數 GHz 的速度透過晶片傳輸訊號而不會產生干擾,同時還可降低功耗。

高 k 值金屬閘極電晶體可改善 DRAM 的 PPAC

DRAM 微縮的第三項關鍵方法是改善晶片週邊邏輯電路所採用電晶體的效能、功耗、面積和成本,以利促進高效能 DRAM (例如基於新型 DDR5 規格之產品) 所需的輸入-輸出 (I/O) 運作效率。

時至今日,DRAM 仍使用複晶矽氧化物材質電晶體,這種材質已在 28 奈米節點的晶圓代工邏輯技術中被淘汰,因為閘極電介質的極薄化會使電子洩漏,進而浪費電力並限制效能。邏輯晶片製造商採用高 k 值金屬閘極 (HKMG) 電晶體,其以金屬閘極與氧化鉿介電質取代複晶矽,而氧化鉿有助於改善閘極電容、防止洩漏和提升效能。現在,記憶體製造商正將 HKMG 電晶體設計導入先進 DRAM 設計,以改善效能、功耗、面積和成本。就邏輯技術而言,HKMG 將在 DRAM 中逐漸取代複晶矽電晶體。

這些在 DRAM 領域中的技術轉折,為應用材料創造了成長機會。較複雜和精密的 HKMG 材料堆疊帶來了製造方面的挑戰,而採用應材的 Endura® Avenir™ RFPVD 系統在真空環境內處理相鄰步驟,已成為業界首選的解決方案。HKMG 電晶體也受益於應材 Centura® RP Epi 等磊晶沉積技術,以及 RadOx™ RTP、Radiance® RTP 及 DPN 等薄膜處理技術,其可用於微調電晶體特性,以利實現最佳效能。

阿丘塔拉曼博士補充:「業界領先的 DRAM 客戶紛紛採用 Draco 硬質光罩和 Black Diamond 低 k 值介電材料,而首批 HKMG DRAM 也已問世。基於上述 DRAM 技術轉變在未來數年間的發展,應用材料預期可增加數十億美元的營收。」

有關上述技術的成長展望,在近期開授的應材「2021 年記憶體大師班」深入介紹。詳細資訊請參閱本公司官網 https://ir.appliedmaterials.com 的投資人關係頁面。

前瞻性陳述

本新聞稿包含某些前瞻性的陳述,包括我們營收、業務與市場所預期的成長及趨勢、產業展望與需求驅動力、技術轉換、新產品和技術,以及其他非歷史實績的陳述。這些陳述或假設的可能受到某些已知或未知的風險或不確定因素影響,並不保證未來績效。這些陳述明示或暗示的內容,可能會與實際結果明顯不符,可能的因素列於應用材料公司提交給美國「證券交易委員會」報告,包括截至最新的 10-Q 及 8-K 表。所有前瞻性的聲明都是截至發稿日為止,依據管理上的估計、預期以及假設所述,本公司並無義務更新這份新聞稿中所提之前瞻性資料。

應用材料公司(那斯達克代號: AMAT)是提供材料工程解決方案的領導者,我們的設備用來製造幾近世界上每顆新式晶片與先進顯示器。我們以工業規模在原子層級進行材料改質的專業,協助客戶將可能轉化成真。在應用材料公司,我們以創新驅動科技,成就未來。欲瞭解更多訊息,請至www.appliedmaterials.com。

# # #

May 11, 2021