半导体 (Semiconductor)

解决方案与软件

赋能 AI 时代

物联网、大数据和人工智能(AI)的兴起,需要快速、大幅改善芯片的功率、性能、面积、成本和上市时间(PPACt™)。这一挑战促使行业制定新的战略;为满足这些需求,整个行业开始以一种新的方式开展协作。 我们将选择并行而非序列性的创新模式,促进整个生态系统更深入广泛地合作,推动从材料到系统(Materials to Systems™)以及从系统到材料(Systems to Materials™)的发展,以加速交付人工智能时代所需的改良型芯片。

PPACt 创新

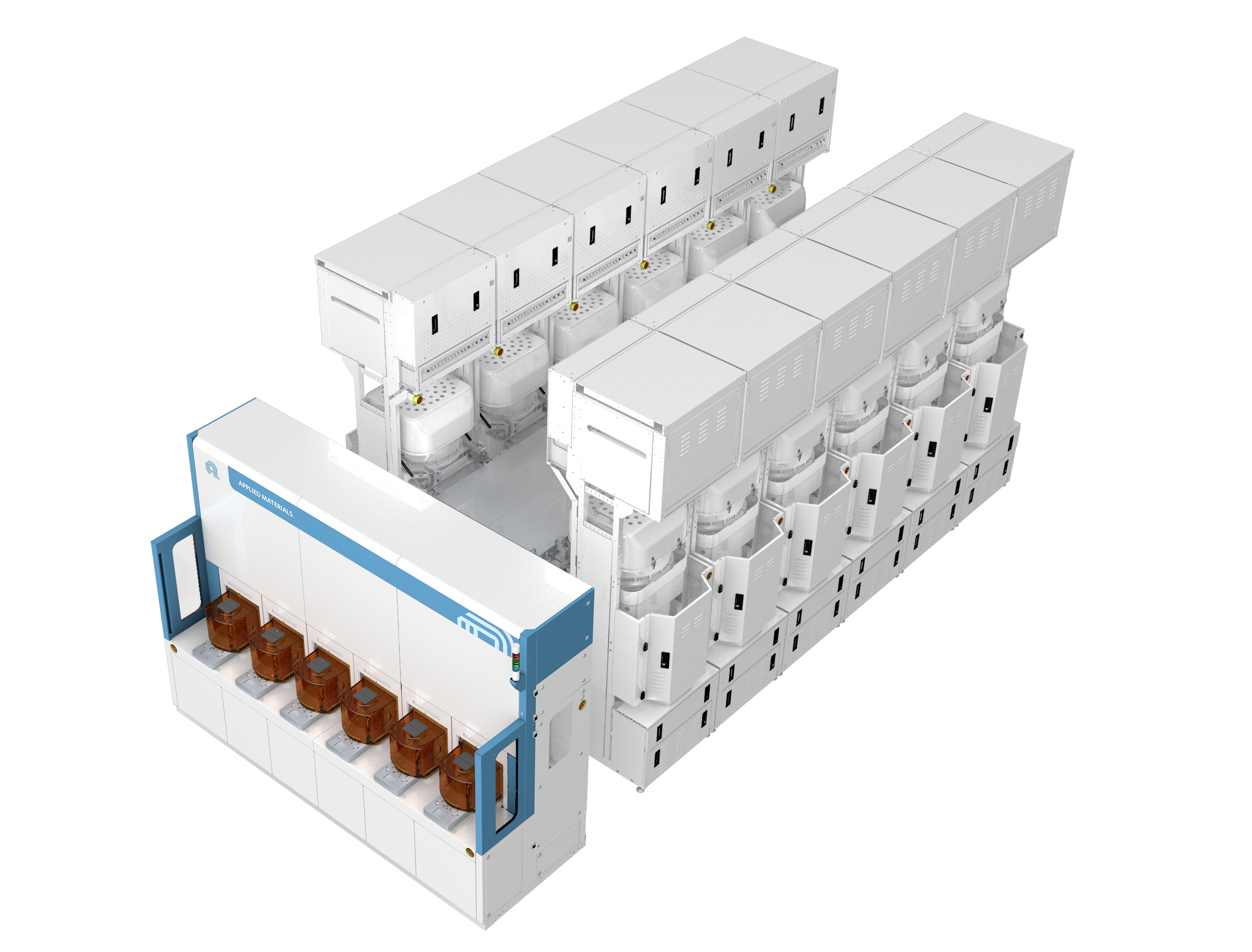

应用材料公司致力于为我们的客户和合作伙伴加速推进这一新的 PPACt 战略。我们拥有广泛精深的产品组合,助力将 PPACt 创新推向市场。这一产品组合能够以新的方式创建和沉积、塑形和去除、改性、分析以及连接材料和器件。应用材料公司的独到之处在于,我们一家厂商即可提供广泛的成套工艺技术和量测设备及服务,并具备能够处理高度细分的各种硅片和封装的实验室能力。我们的 Integrated Materials Solution®(集成材料解决方案)技术对材料的沉积、去除、改性和分析进行同步优化,以形成新的材料,并能在前沿节点上设计打造高性能、低功耗芯片所需的新结构。

加速实现净零排放

我们的系统经久耐用,可支持新应用的升级和改动,在出现部件故障或性能低于可接受标准时易于维修。所有新制造的部件都经过精心设计,更容易维修,我们在维修和再制造中尽可能使用翻新部件,从而提高生产可持续性和成本效益。我们认为,拥有业内独特的领导地位即意味着要对员工、客户和社会承担起巨大的责任。这就是为什么,我们的系统从设计建造开始就考虑绿色环保,因为我们都在朝着净零排放的目标迈进,实现更加美好的未来。

Building on an Unmatched Foundation of CVD Innovation

Applied Materials Earns Intel’s 2024 EPIC Distinguished Supplier Award

Collaboration is Key to Enabling Advanced Patterning in the Angstrom Era