半导体 (Semiconductor)

解决方案与软件

设计和制造用于生产半导体芯片的系统

赋能 AI 时代

人工智能时代要求芯片的能效和性能实现快速、显著的提升。这一挑战是应用材料公司以新的方式开展创新与协作,加速新技术商业化的愿景背后的驱动力。通过在整个生态系统内进行协作,我们能够为人工智能时代提供更优质的芯片。

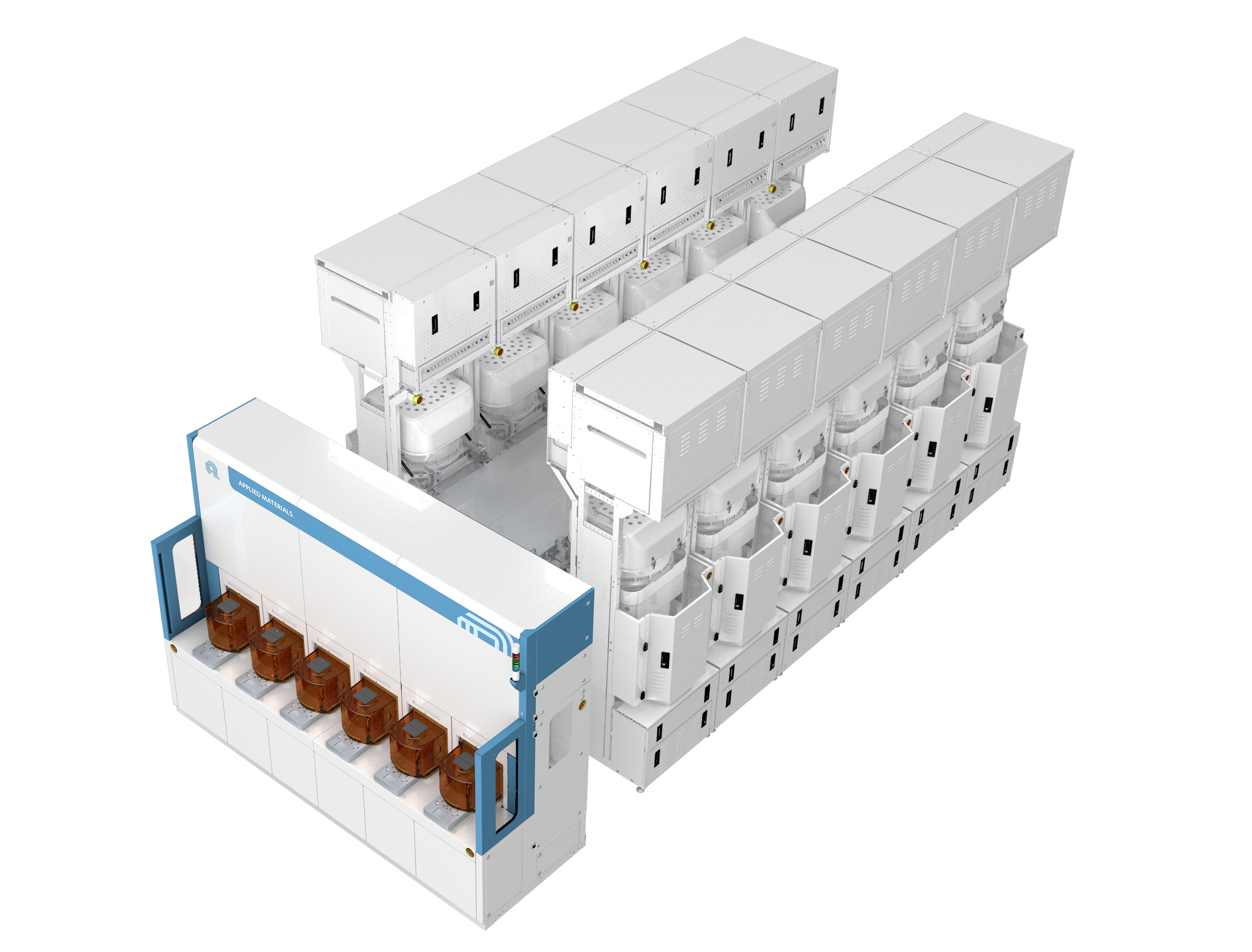

突破性创新

通过连接我们广泛的能力和技术组合,我们开发了高度差异化的解决方案。我们的产品种类繁多且相互关联,能以新的方式形成和沉积、塑造和去除、改性、分析以及连接材料与设备。我们的 "集成材料解决方案"(Integrated Materials Solution®)技术整合了一整套工艺技术和量测能力,对材料沉积、移除、改性和分析进行了协同优化,从而能在前沿节点上为高性能、低功耗芯片形成新材料、构建新结构。

可持续加速

我们的系统设计经久耐用,支持升级和用于新应用的重新改造。所有新生产的系统组件和部件都经过精心设计,具有更高的可维修性,我们还尽可能使用翻新部件,以实现可持续发展,降本增效。我们正在持续开发更多面向晶圆厂和子晶圆厂的技术与服务,以提升客户运营的可持续性。我们认识到,我们独特的领导地位伴随着我们对员工、客户和社会的巨大责任。

Applied Materials Earns TSMC’s Excellent Performance Awards

The ecoUP™ Portfolio: Paving the Path to a Sustainable Future

CTO Omkaram Nalamasu Receives ACS Award in Industrial Chemistry