製品・サービス

製品・サービス

トレンド

Going “All In”: How Applied Materials is Turning Hunger into Hope

Precision from the Bottom Up: Enabling Angstrom-Era AI with Sym3™ Z Magnum™

アプライド マテリアルズ サプライヤーエクセレンス賞を発表

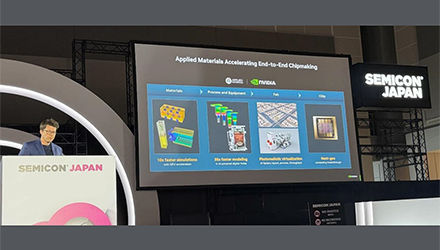

Applied Materials Collaborates With NVIDIA to Accelerate End-to-End Chip Manufacturing