半导体 (Semiconductor)

技术

-

ALD

-

CMP

-

CVD(化学气相沉积)

-

ECD

-

外延生长

-

刻蚀

-

离子注入

-

测量与检测

-

Pattern Shaping

-

光掩膜

-

PVD(物理气相沉积)

-

快速热处理(RTP)

-

模拟

-

化合物半导体

-

微机电系统(MEMS)

-

功率

晶圆制造厂环境解决方案

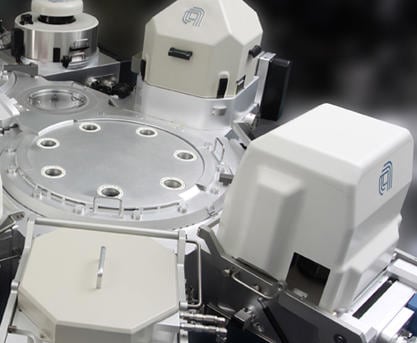

Endura™ iLB™ PVD/ALD

随着器件尺寸缩小,而集成式衬垫/阻挡层 (iLB) 厚度消耗更多的钨插头体积,接触电阻在不断增加,造成相应的困难;应用材料公司配备 Centinel™ 沉积室的 Endura iLB PVD/ALD 系统解决了这一难题。

该系统以低成本高效的方式利用 ALD(原子层沉积)技术,通过 90% 以上覆盖超薄、均匀、优质的阻挡膜,将客户现有的 iLB PVD/CVD 安装基础扩展至 32nm 及之上。 它在沉积 TiN 膜时将等离子损伤或高介电材料属性不利变化的风险降到最小,从而支持先进的内存应用。

Centinel 技术通过 RE-ALD 室(经原子团增强的原子层沉积室)增强了 Endura iLB 集成式 PVD/CVD(物理气相沉积/化学气相沉积)工艺平台,通过实现 32nm 以下逻辑器件中更小的接触电阻而优化钨体积。它也设计用于 4X 节点嵌入式 DRAM、DRAM 电极和掩埋字线应用。

Centinel 工艺实现的出色阶梯覆盖能使阻挡层厚度最小化,从而优化均匀沉积的内部特性。除了使钨填充可用的体积最大化之外,阻挡层的极限厚度减少了加工每枚硅片所需的时间,并有助于提高生产率。由于不发生背面沉积,生产率不受背面清洁的不利影响。另一项好处是沉积室工作的加工温度更低,从而减少对高介电材料的再结晶损害。