半導體 (Semiconductor)

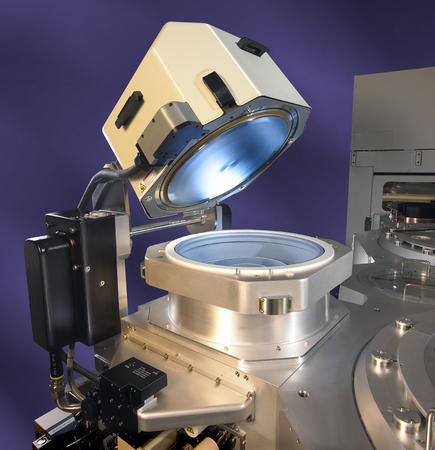

Endura® ALPS® PVD (ALPS Co & Ni)

應用材料的 Endura 先進低壓源 (ALPS) 鈷物理氣相沉積 (PVD) 系統針對高深寬比結構中的閘極和觸點,提供簡單、高效能的矽化層解決方案。ALPS 技術將鈷延伸應用在 ≤90nm 以下技術節點,可提供優異的鈷底部覆蓋,且電漿不會對元件造成損壞,缺陷數量極少。Endura ALPS Co 提供出色的電阻性、低漏電流和熱穩定效能,解決了鈦集聚、接觸點電阻變化和摻雜物吸除等難題。

對於 65nm/55nm 及以下的邏輯和記憶體應用,鈷的矽消耗和矽化鈷/矽介面的粗糙度變得更加關鍵。Endura ALPS Ni PVD 系統可沉積穩定的矽化鎳薄膜,使矽消耗量減少 2 倍,薄膜介面更平滑且電阻率更低。ALPS Ni 可達到 100Å 底部覆蓋,且電漿不會對元件造成損壞,同時微粒數量還能降至最低。

Applied Endura ALPS Ni PVD 系統採用單反應室 Siconi Preclean 預潔淨介面工程技術,解決了矽化鎳 (NiSi) 成形前的矽清潔表面處理難題。Siconi Preclean 預潔淨技術可提供高選擇性清洗 (大於 20:1 SiO2:Si, >5:1 SiO2:SiN);但和傳統氫氟酸清潔製程不同的是,此技術在清潔和鎳沉積之間無需緊密的等候時間控制。在遠端電漿源中產生蝕刻液,能大幅降低對基板的損害,且產生最少的蝕刻特性 (如氮隔離層和矽閘極)。此外,根據元件研究顯示,相較於傳統氫氟酸溶液清洗流程,採用 Siconi Preclean 預潔淨技術能減少 NiSi2 尖形缺陷,並且降低接面漏電。