Back to Menu

반도체

Enabling the AI Era

The Internet of Things, Big Data and artificial intelligence (AI) demand rapid, dramatic improvements in chip power efficiency, performance, area, cost, and time to market (PPACt™). This challenge is the force behind our industry’s new playbook; to meet these demands the entire industry is beginning to collaborate in a new way. We are choosing parallel innovation over serial innovation and promoting greater collaboration across the ecosystem—from Materials to Systems™ and from Systems to Materials™—to accelerate the delivery of improved chips for the AI era.

PPACt Innovations

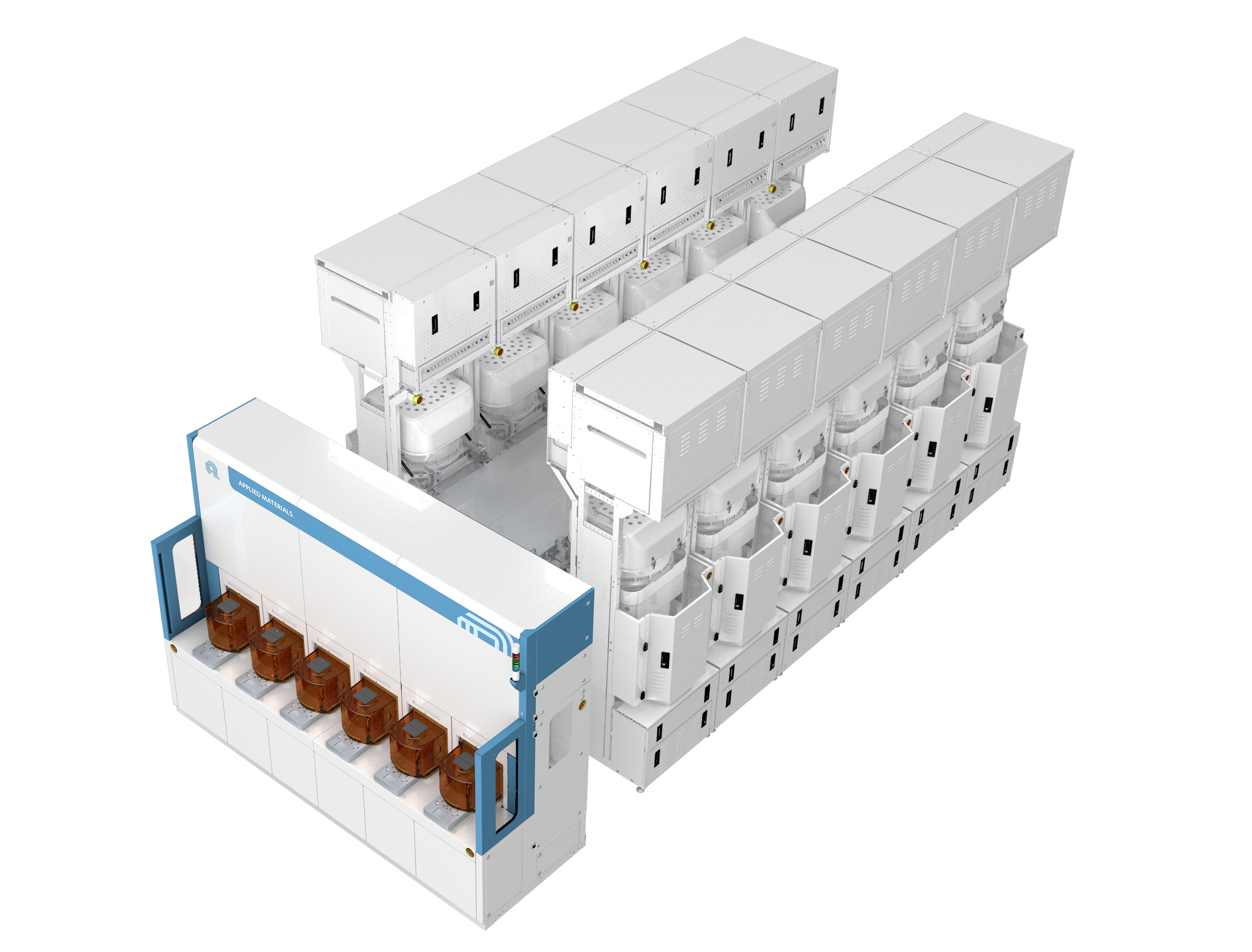

Applied Materials is committed to accelerating the new PPACt playbook for our customers and partners. We have the broadest and deepest portfolio of products for delivering PPACt innovations to the market. This portfolio encompasses the ability to create and deposit, shape and remove, modify, analyze, and connect materials and devices in new ways. We are unique in having a broad suite of process technology and metrology capabilities under one roof, and we have highly differentiated silicon and packaging lab capabilities. Our Integrated Materials Solution® technologies co-optimize materials deposition, removal, modification, and analysis to create new materials and engineer new structures for high-performance, low-power chips at leading-edge nodes.

Net Zero Acceleration

Our systems are designed to last, to support upgrades and repurposing for new applications, and to be easily repairable if parts fail or performance falls below acceptable standards. All newly manufactured parts are engineered for greater repairability, and we use refurbished parts whenever possible for repair and remanufacture, contributing to sustainability and cost-effectiveness. We recognize that our unique leadership position comes with tremendous responsibility to our employees, customer and society, which is why our systems are built green from the start as we all march towards our net zero initiatives and Make Possible a Better Future.

Building on an Unmatched Foundation of CVD Innovation

Applied Materials Earns Intel’s 2024 EPIC Distinguished Supplier Award

Collaboration is Key to Enabling Advanced Patterning in the Angstrom Era